# <u>Final Report</u> "Advanced Modeling and Test Methods for Radiation Effects on Microelectronic Devices"

Dr. Robert A. Reed and Dr. Robert A. Weller

Electrical Engineering and Computer Science Department Institute for Space and Defense Electronics 2014 Broadway, Suite 200 Nashville, TN 37203 USA

> Tel (615) 343-2702 / FAX (615) 343-9550 email: <u>robert.reed@vanderbilt.edu</u> <u>robert.a.weller@vanderbilt.edu</u>

> > NASA Goddard Contact:

Ken Label NASA Goddard Space Flight Center Code 562, Greenbelt, MD 20771 Phone: (301) 286-2153

02/29/2008

# "Advanced Modeling and Test Methods for Radiation Effects on Microelectronic Devices" Co-Investigators: Dr. Robert Reed and Dr. Robert Weller Vanderbilt University Electrical Engineering and Computer Engineering Department

# Abstract/summary:

The safety of human and robotic missions depends critically upon the reliability of electronic systems. Space radiation effects are among the greatest environmental threats to the safety of manned and robotic missions. Take, for example, life support electronics. While the crew on a manned mission may be well protected from radiation hazards, the critical life support electronics may be near the skin of the craft and relatively unprotected. Radiation effects in electronics range from loss of data to catastrophic failure. In advanced electronics, effects caused by the passage of a single energetic particle through a sensitive device are the most serious problem; while many different electrical effects have been observed, these phenomena are collectively described as single-event effects (SEEs).

Radiation effects data from newer devices, including such essential components as fiber optic systems and state-of-the art digital/mixed signal electronics, have demonstrated that existing models have significant errors. For example, using CREME96 for optocouplers underestimates single event rates, overestimating survivability. Standard models also produce inaccurate estimates for single event rates in SiGe, CMOS technologies and low-dose-rate degradation of bipolar linear ICs.

The safety and reliability of forthcoming long-duration missions will depend critically on using the most advanced electronics available and providing radiation/fault-tolerant system design. Advances in microelectronic technologies have created a situation in which time-tested methodologies for radiation-hard electronic design, validation, and verification can no longer assure the safety of electronic parts and systems used for space exploration. Therefore, a new tool is needed so that the reliability and safety of space systems can be assessed. This tool must be based upon first-principles physics computations so that engineers can predict accurately the radiation tolerance of emerging technologies in the space environment.

The objective of the current proposal is to continue to develop new technology modeling approaches for radiation induced Single Event Transients (SETs) in photodetectors and advance CMOS devices and Single Event Upsets (SEUs) in Silicon Germanium (SiGe) Heterojunction Bipolar Transistors (HBTs) and advanced CMOS devices. We will continue to develop a technology model testbed that integrates detailed transport physics models with device physics models and approximation models. This testbed will be extendable to many other technologies.

# **Background**

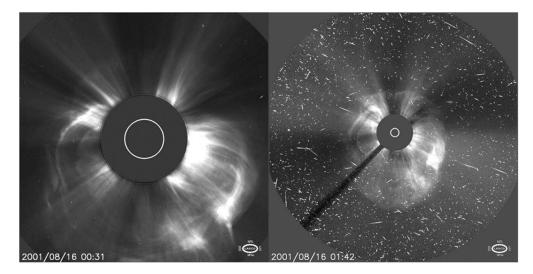

NASA and DOD spaceflight missions often rely on system level solutions to mitigate the impact of a single microelectronic component failure due to exposure to the space radiation environment. This has proven to be a very effective and useful approach. These techniques range from the use of error correction techniques for data memory to redundant subsystems. In some drastic cases, system engineers have opted to power down subsystems during times when the radiation environment is severe—preventing data collection or posing significant risk to the subsystem. An example of the latter is the NICMOS instrument on the Hubble Space Telescope; radiation events in a microelectronic device require instrument operation to be discontinued while passing through the South Atlantic Anomaly region of the earth trapped radiation

environment<sup>1</sup>. A detailed understanding of the reliability/survivability of microelectronic devices when exposed to the space radiation environment is critical for sound system engineering decisions.

The success of a system engineering approach to radiation-effects analysis depends on the following factors: 1) A conservative model of the radiation environment for evaluating the extent to which radiation threats may compromise mission goals. 2) Measurements of component responses to terrestrial radiation sources for bounding on-orbit device performance. 3) A comprehensive physical model to predict the energy deposited in the semiconductor by terrestrial and space radiation sources. 4) Physics-based component response models to predict and analyze electrical performance degradation.

The success of such analysis depends critically on the models used for the interaction and transport of radiation through spacecraft structures and semiconductor materials. These models serve as a bridge between ground-based laboratory data and prediction of on-orbit radiation performance. They also provide guidance as to the test methods and laboratory measurements needed for such predictions.

Advances in microelectronic technologies and economic pressure to use commercial electronic parts have created a new situation in which time-tested methodologies for radiationhard electronic design, validation, and verification can no longer assure the safety (as defined in NFS 1852.223-70) of electronic parts and systems used for space exploration. In particular, several recent developments<sup>2</sup> suggest that it may be appropriate to revisit the methods and models used in predicting on-orbit radiation response of modern electronics and advanced sensors. Recent radiation effects experiments on these modern technologies show trends inconsistent with current models: 1) SiGe HBTs, 2) large scale photodetectors, 3) SOI/SOS CMOS, 4) IR Focal Plane Arrays (FPAs), 5) CCDs, and 6) advanced CMOS. In particular the existing models have the following shortcomings:

- Exclude combined effects from direct and indirect ionization by incident particles

- Do not account for the angular dependence of the recoiling nuclei produced by protoninduced spallation reactions or elastic collisions

- Exclude the charge collection by diffusion

- Have limited capability to analyze detailed geometrical effects, i.e., edge effects, isolation trenches, buried oxides

- Have no method for modeling effects associated with the complex spatial variation of charge deposited by individual ion strikes.

The simple truth is that the existing techniques, developed circa 1980, fail to provide accurate reliability/survivability estimates for most modern technologies. Mature technologies have been scaled to dimensions where new phenomena challenge some of the basic simplifying assumptions of radiation effects models, which were developed for technologies fabricated in the late 70's early 80's. Some recent results suggest that current methods could yield predictions that overestimate or underestimate on-orbit error rates by an order of magnitude or more.

# **Technical Approach**

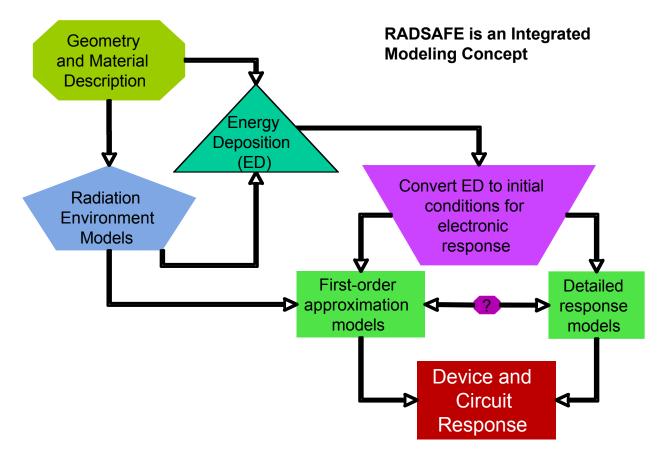

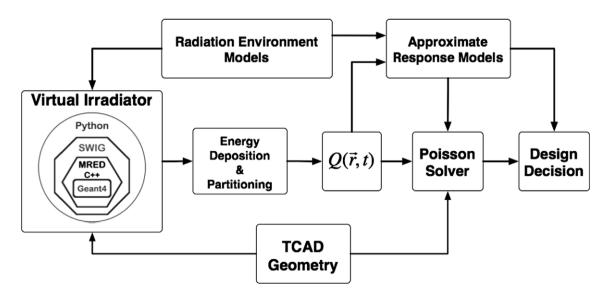

Our approach is focused on the end goal of developing a fully-automated first-principles predictive tool that is based on the best available physics for radiation transport and microelectronic device performance. This is a Monte Carlo approach that combines three distinct concepts: 1) transport of the radiation environment though the component and relevant surrounding materials, 2) first-order approximation to estimate the response of the technology to

radiation exposure, and 3) deterministic simulation of the detailed component response to radiation exposure.

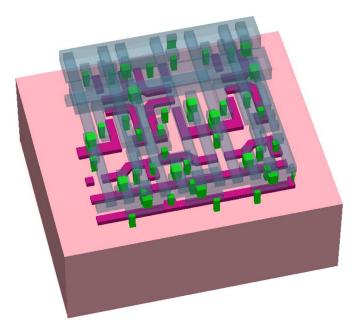

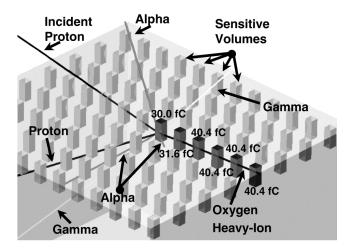

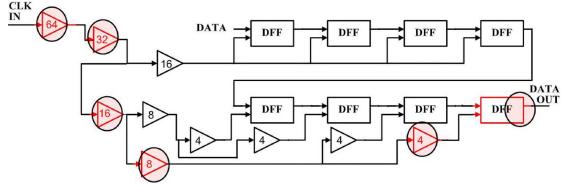

Figure 3: Conceptual diagram of the technology modeling approach

The first segment builds on existing, reliable, and well-calibrated computational physics models for the transport of radiation through matter (e.g., Geant4). Geant4 is a set of c++ class libraries for building high-energy physics detector simulation codes. Its development is coordinated by the European Laboratory for Particle Physics, CERN, in Switzerland, and is supported by the Stanford Linear Accelerator Center (SLAC), the European Space Agency (ESA), the medical physics community, and others. The stated objective for Geant4 is that it will encompass all that is known about the interactions of radiation with matter, and to do it in an extensible and flexible implementation. Because of its wide acceptance by users, who provide validation in many ways, the large and active development community, and available source code, it is an ideal component for this program. A major component of our work will be to validate the Geant4 routines for application to radiation effects in microelectronics.

The second segment is accomplished by first uncovering the basic mechanisms for the device/circuit SEE response using detailed device physics simulators (e.g., ISE's DESSIS software or Silvaco's ATLAS software) and ground based experimental data. From this understanding, we develop a first-order Quasi-Device Physics (QDeP) model for the response. QDeP models are technology dependent, can either be analytical or Monte Carlo models, account for both the energy deposition in semiconductor by the radiation event and the device response to this event, and must always over estimate the effects of radiation. The QDeP estimate allows for timely and accurate computational analysis of the device response using the

third segment by selecting only those events that have a high probability of causing an effect. (Note: Once fully developed the QDeP model for each technology can be used in a system level on-orbit predictive tool development. This new QDeP models will replace the classical models like those used in the CREME96 routines for heavy ion effects.)

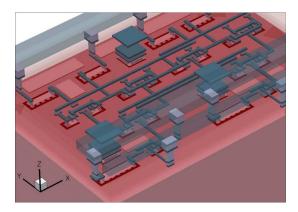

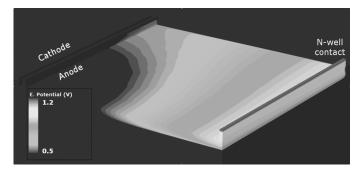

The third segment applies TCAD tools like DESSIS (DEvice Simulation for Smart Integrated Systems) from Integrated Systems Engineering (ISE) to deterministically predict the device response to the radiation event. The approach is to build a Geant4 module for generating selected events in simple planar structures that are similar to the structures used to build the device in DESSIS. The energy deposition is computed in detail and the device response is predicted by full 3D mixed mode simulations.

The development of appropriate QDeP technology model will be dynamic feedback from the third segment. The results of the third segment will be used to improve the QDeP models. This will be done manually at first. However, it is obvious that techniques can be developed to automate this procedure for developing more accurate QDeP models.

Full automation and integration of each segment with the others is an area of active research. Integration cannot be completed during this grant's period of performance. However, we will develop an implementation plan for this integration.

# <u>Tasks</u>

# Task #1. Validation of Geant4 radiation transport model for space applications CMOS

The physical processes modeled by Geant4 are well calibrated against experimental data collected with the interests of developing a better understand of high-energy physics. These models should be applicable to the species and energies of interest when studying radiation effects in microelectronics. However there are certain modeling and particle tracking routines that that must be validated for application to radiation effects in microelectronics.

This past two years we complete the following research:

- We will perform a literature search to uncover published experimental results describing electronic and nuclear interactions of ions in matter that is consistent with space radiation effects on microelectronics

- We will collect certain experimental validation data as needed

- We will perform detailed Geant4 simulations that are consistent with the experiments setups and compare our results to the experimental data

- We will report findings to the Geant4 development team (SLAC and ESA) and support them to improve models were needed

# Technical Reports and Presentations:

- R. A. Reed, R. A. Weller, M. H. Mendenhall, J.-M. Lauenstein, K. M. Warren, J. A. Pellish, R. D. Schrimpf, B. D. Sierawski, L. W. Massengill, P. E. Dodd, M. R. Shaneyfelt, J. A. Felix, J. R. Schwank, N. F. Haddad, R. K. Lawrence, J. H. Bowman, R. Conde, "Impact of Ion Energy and Species on Single Event Effects Analysis," IEEE Trans. Nuc. Sci., vol. 54, no. 6, pp. 2312 - 2321, 2007.

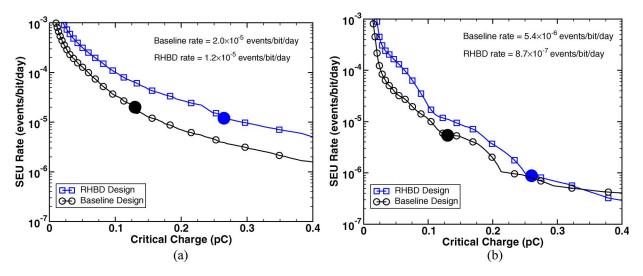

- J. A. Pellish, R. A. Reed, A. K. Sutton, R. A. Weller, M. A. Carts, P. W. Marshall, C. J. Marshall, R. Krithivasan, J. D. Cressler, M. H. Mendenhall, R. D. Schrimpf, K. M. Warren, B. D. Sierawski, G. F. Niu, "A Generalized SiGe HBT Single-Event Effects Model for On-Orbit Event Rate Calculations," IEEE Trans. Nuc. Sci., vol. 54, no. 6, pp. 2322 2329, 2007.

- (Outstand Conference Paper) P. E. Dodd, J. R. Schwank, M. R. Shaneyfelt, J. A. Felix, P. Paillet, Ferlet- V. Cavrois, J. Baggio, R. A. Reed, K. M. Warren, R. A. Weller, R. D. Schrimpf, G. L. Hash, S. M. Dalton, K. Hirose, H. Saito, "Impact of Heavy Ion Energy and Nuclear Interactions on Single-Event Upset and Latchup in Integrated Circuits," IEEE Trans. Nuc. Sci., vol. 54, no. 6, pp. 2303 - 2311, 2007.

- 4. R. D. Schrimpf, R. A. Weller, M. H. Mendenhall, R. A. Reed, and L. W. Massengill, "Physical Mechanisms of Single Event Effects in Advanced Microelectronics," Nucl. Inst. Meth. B, vol. 261, no. 1-2, 2007, p 1133-6.

- R. A. Reed, R. A. Weller, R. D. Schrimpf, M. H. Mendenhall, K. M. Warren, and L. W. Massengill, "Implications of Nuclear Reactions for Single Event Effects Test Methods and Analysis," IEEE Trans. Nucl. Sci., vol. 53, no. 6, pp. 3356-3362, 2006.

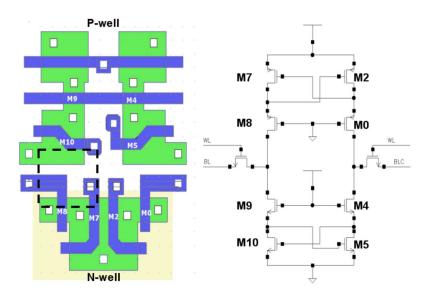

- D. R. Ball, K. M. Warren, R. A. Weller, R. A. Reed, A. Kobayashi, J. A. Pellish, M. H. Mendenhall, C. L. Howe, L. W. Massengill, R. D. Schrimpf, N. F. Haddad, "Simulating Nuclear Events in a TCAD Model of a High-Density SEU Hardened SRAM Technology," IEEE Trans. Nucl. Sci., vol. 53, no. 4, pp. 1794-1798, 2006.

- R. A. Reed, R. A. Weller, M. H. Mendenhall K. M. Warren D. R. Ball, J. A. Pellish B. D. Sierawski C. L. Howe, L. W. Massengill, R. D. Schrimpf, M. Alles, A. L. Sternberg, A. F. Witulski, A. D. Tipton, K. A. LaBel, M. A. Xapsos, P. W. Marshall, J. H. Adams, N. F. Haddad, J. Bowman, R. Lawrence, M. Porter, J. Wilkinson, T. Hoang, C. Carmichael, H. Wan, A. Lesea, J.L. de Jong and R. Padovani. "Applications of RADSAFE" presented at SEE Symposium 2007, Long Beach, CA, April, 2007

- R. A. Reed, R. A. Weller, R. D. Schrimpf, L. W. Massengill, M. H. Mendenhall, K. M. Warren, B. Sierawski, D. R. Ball, M. Alles, A. Sternberg, J. A. Pellish, C. Howe, A. Tipton, "Single Event Effects Analysis," New Electronic Technologies Insertion into NASA Flight Programs, Greenbelt, MD, 2007.

# While not directly funded by NEPP, this work was enabled by the validation and development of our Geant4 application MRED:

- K. M. Warren, B. D. Sierawski, R. A Weller, R. A. Reed, M. H. Mendenhall, J. A. Pellish, R. D. Schrimpf, "Predicting Thermal Neutron Induced Soft Error in Static Memories Using Monte-Carlo Simulations" IEEE Electron Device Lett. vol. 28, no. 2, pp. 180–182, 2007.

- K. M. Warren, J. D. Wilkinson, S. Morrison, R. A. Weller, M. E. Porter, B. D. Sierawski, R. A. Reed, M. H. Mendenhall, R. D. Schrimpf, and L. W. Massengill, "Modeling Alpha and Neutron Induced Soft Errors in Static Random Access Memories," in Proc. IEEE International Conference on Integrated Circuit Design and Technology, 2007, pp. 217-220.

- J. Wilkinson, M. Porter, S. Morrison, R. A. Reed, B. Sierawski, K. Warren, R. Weller, and M. Medenhall, "Ion Microprobe Measurements of Sensitive Volumes in a 0.25μm CMOS Flip-flop", presented at the 2nd Workshop on System. Effects of Logic Soft Errors, Urbana-Champaign, Ill, April 13-14, 2007.

# Task #2. Radiation Effects in Texas Instruments CMOS Devices

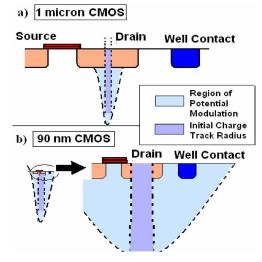

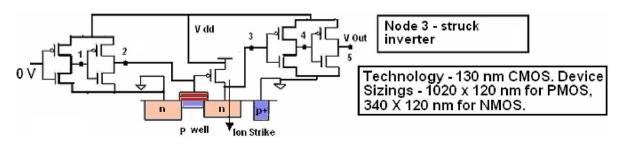

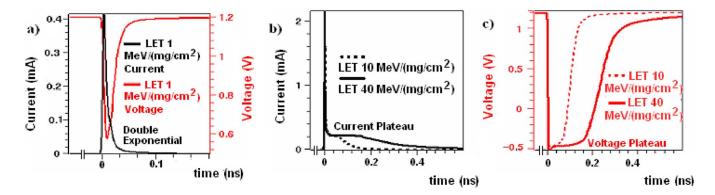

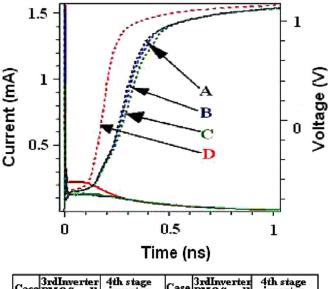

The effects of ion-induced charge collection in ultra-scaled CMOS technologies (130 nm and below) can be investigated by combining two research techniques: 1) measurement and modeling of single-event charge liberation via Ion Beam Induced Charge Collection (IBICC) and/or Laser Induced Charge Collection (LICC) on simple structures (e.g., transistors, diodes, inverters) or 2) single event effect measurement and modeling of ring oscillators (RO) fabricated in those advanced technologies. The first method gives a method for a detailed understanding of the basic charge collection mechanisms. The second method will allow for an understanding of the sensitivity of the technology in a real circuit.

This past two years we complete the following research:

- Develop detail radiation transport, device physics, and QDeP models to better understand the dynamics of charge collection and circuit response to radiation.

- Note that IBICC and LICC is funded by DTRA under an MRC agreement

Technical Reports and Presentations:

- S. DasGupta, A. F. Witulski, B. L. Bhuva, M. L. Alles, R. A. Reed, O. A.Amusan, J. R. Ahlbin, R. D. Schrimpf, L. W. Massengill, "Effect of Well and Substrate Potential Modulation on Single Event Pulse Shape in Deep Submicron CMOS," IEEE Trans. Nuc. Sci., vol. 54, no. 6, pp. 2407 2412, 2007.

- K. M. Warren, R. A. Weller, B. Sierawski, R. A. Reed, M. H. Mendenhall, R. D. Schrimpf, L. W. Massengill, M. Porter, J. Wilkinson, K. A. LaBel, and J. Adams, "Application of RADSAFE to Model Single Event Upset Response of a 0.25 μm CMOS SRAM," IEEE Trans. Nuc. Sci., vol. 54, no. 4, pp. 898 -903, 2007.

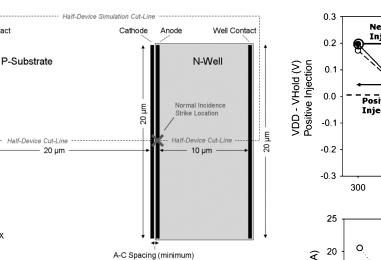

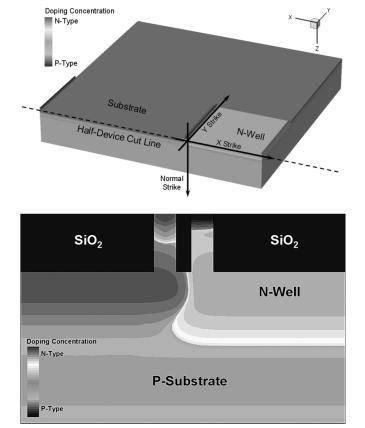

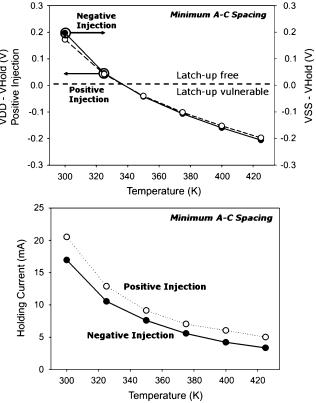

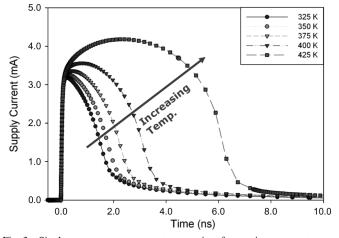

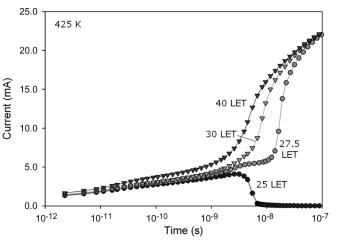

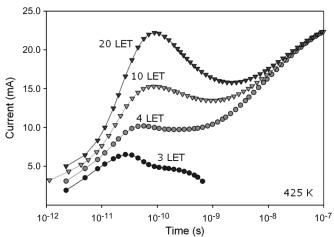

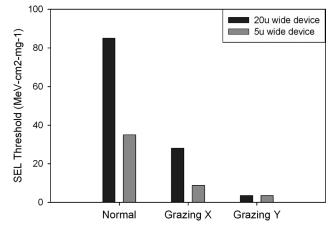

- J. M. Hutson, J. D. Pellish, G. Boselli, R. Baumann, R. A. Reed, R. D. Schrimpf, R. A. Weller, L. W. Massengill, "The Effects of Angle of Incidence and Temperature on Latchup in 65 nm Technology," IEEE Trans. Nuc. Sci., vol. 54, no. 6, pp. 2541 - 2546, 2007.

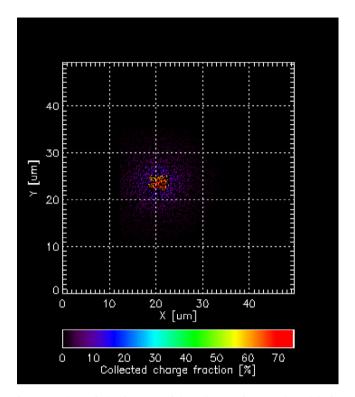

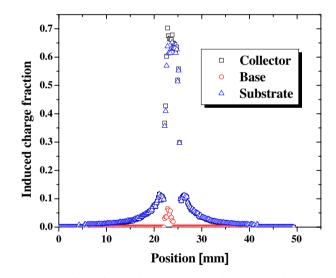

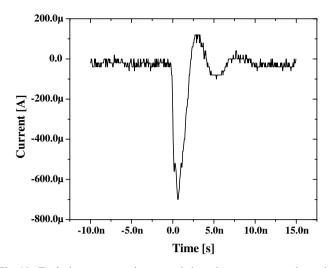

- R. A. Reed, G. Vizkelethy, J. A. Pellish, B, Sierawski, K. M. Warren, M. Porter, J. Wilkinson, P. W. Marshall, G. Niu, J. D. Cressler, R. D. Schrimpf, A. Tipton, and R. A. Weller, "Applications of Heavy Ion Microprobe for Single Event Effects Analysis," Nucl. Inst. Meth. B, vol. 261, no. 1-2, 2007, pp. 443-6.

- A. D. Tipton, J. A. Pellish, R. A. Reed, R. D. Schrimpf, R. A. Weller, M. H. Mendenhall, B. Sierawski, A. K. Sutton, R. M. Diestelhorst, G. Espinel, J. D. Cressler, P. W. Marshall, and G. Vizkelethy, "Multiple-Bit Upset in 130 nm CMOS Technology," IEEE Trans. Nucl. Sci., vol. 53, no. 6, pp. 3259-3264, 2006.

- A. D. Tipton, J. A. Pellish, P. R. Fleming, R. D. Schrimpf, R. A. Reed, R. A. Weller, M. H. Mendenhall, and L. W. Massengill, "High Energy Neutron Multiple-Bit Upset," in Proc. IEEE International Conference on Integrated Circuit Design and Technology, 2007, pp. 210-212.

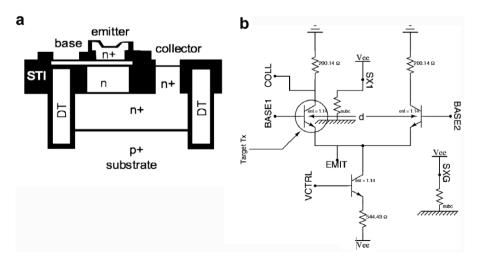

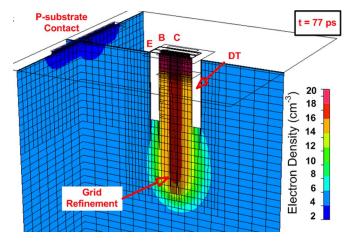

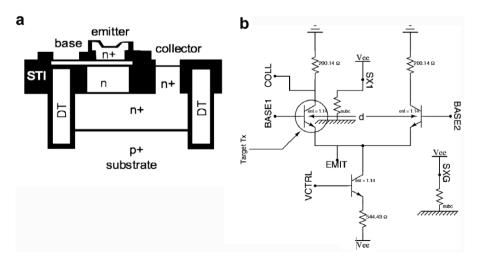

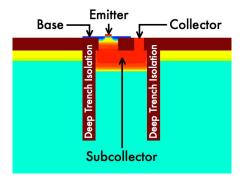

# Task #3. Radiation Effects in SiGe HBTs

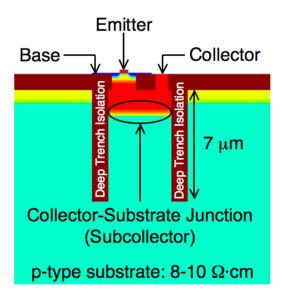

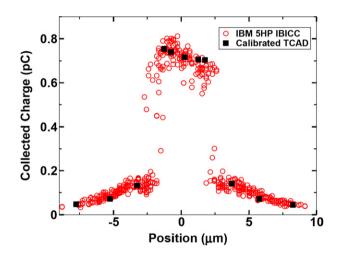

VU/ISDE continued to develop a basic understanding of the mechanisms for inducing SEU/SETs in HBTs,. This year we will focused our efforts on full TCAD simulation of the device and circuit response for 5HP and 8HP technologies. We also focused on experimental measurements of current pulse and charge collection.

This past two years we complete the following research:

- Finalize first-order model and test method for IBM 5HP BiCMOS technology

- Begin study to extended first-order model to 7HP and 8HP.

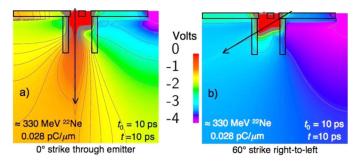

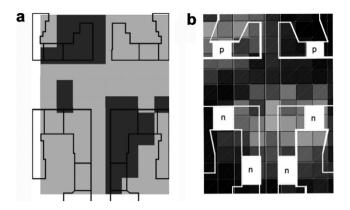

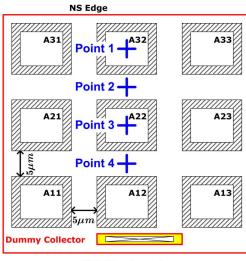

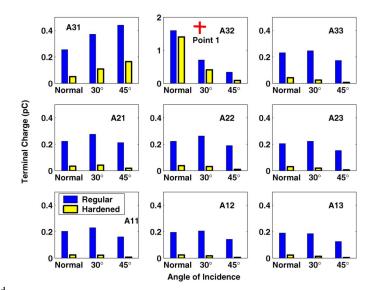

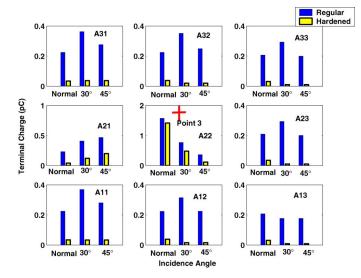

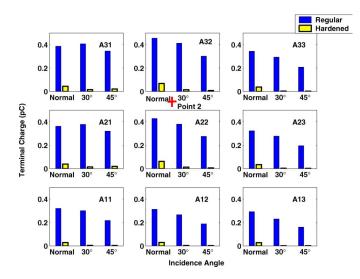

- Use TCAD to predict the angular response of HBT devices to all events at various locations and angles across the entire device and compare this to microbeam results.

- Begin full circuit simulations to model the angle dependence of the broadbeam cross section.

- Microbeam and broadbeam testing support

# Technical Reports and Presentations:

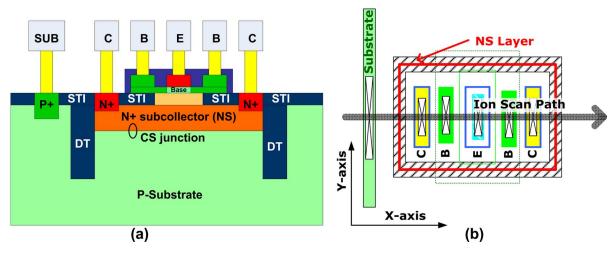

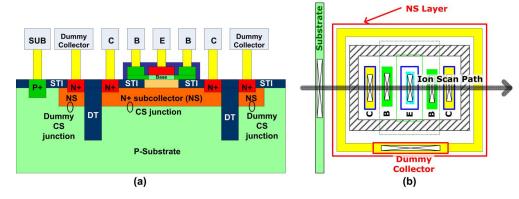

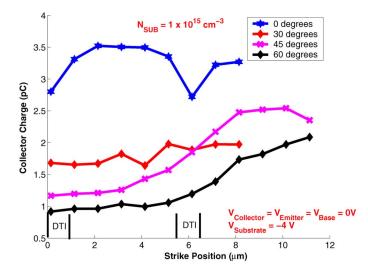

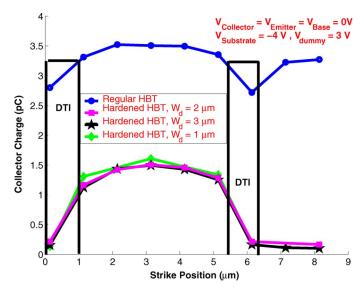

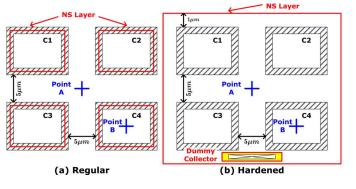

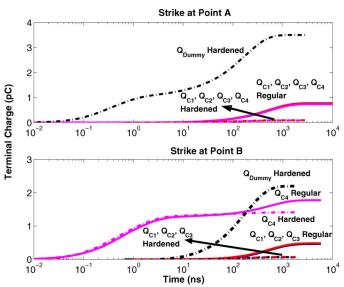

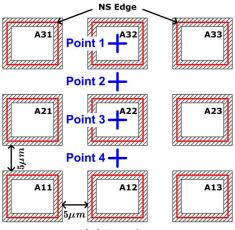

- M. Varadharajaperumal, G. Niu, X. Wei, T. Zhang, J. D. Cressler, R. A. Reed, P. W. Marshall, "3-D Simulation of SEU Hardening of SiGe HBTs Using Shared Dummy Collector," IEEE Trans. Nuc. Sci., vol. 54, no. 6, pp. 2419 - 2425, 2007.

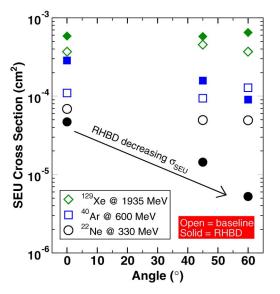

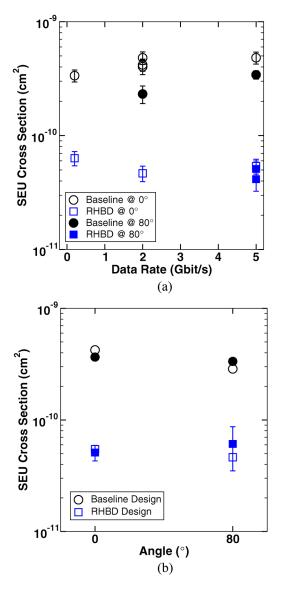

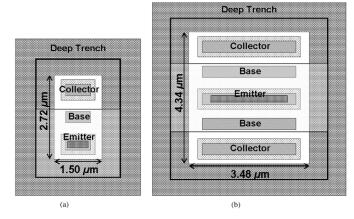

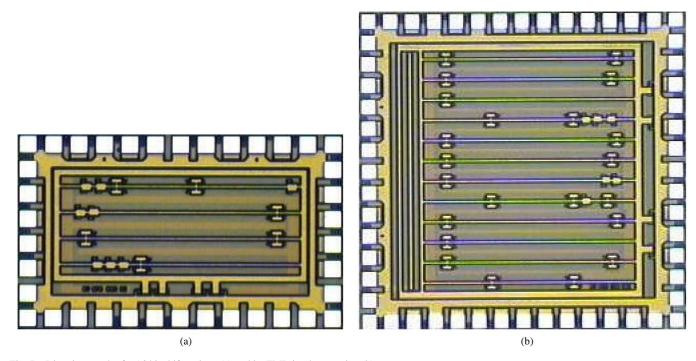

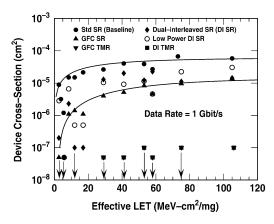

- [2] A. K. Sutton, M. Bellini, J. D. Cressler, J. A. Pellish, R. A. Reed, P. W. Marshall, G. Niu, G. Vizkelethy, M. Turowski, A. Raman, "An Evaluation of Transistor-Layout RHBD Techniques for SEE Mitigation in SiGe HBTs," IEEE Trans. Nuc. Sci., vol. 54, no. 6, pp. 2044 - 2052, 2007.

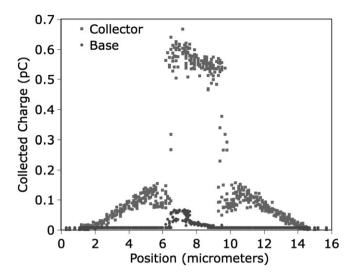

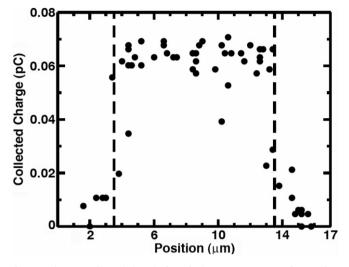

- [3] G. Vizkelethy, R. A. Reed, P. W. Marshall, J. A. Pellish, "Ion beam induced charge (IBIC) studies of silicon-germanium heterojunction bipolar transistors (HBTs)," Nucl. Inst. Meth. B, vol. 260, no. 1, 2007, p 264-9.

- [4] R. A. Reed, G. Vizkelethy, J. A. Pellish, B, Sierawski, K. M. Warren, M. Porter, J. Wilkinson, P. W. Marshall, G. Niu, J. D. Cressler, R. D. Schrimpf, A. Tipton, and R. A. Weller, "Applications of Heavy Ion Microprobe for Single Event Effects Analysis," Nucl. Inst. Meth. B, vol. 261, no. 1-2, 2007, pp. 443-6.

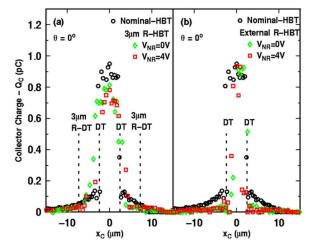

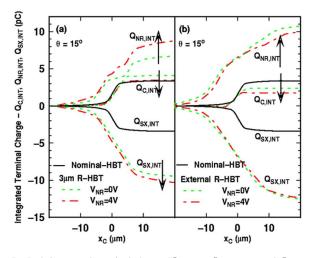

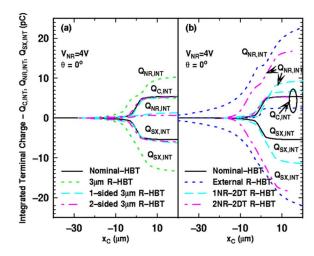

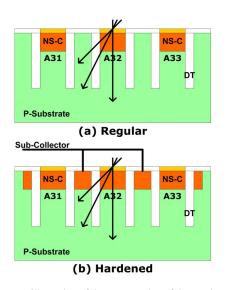

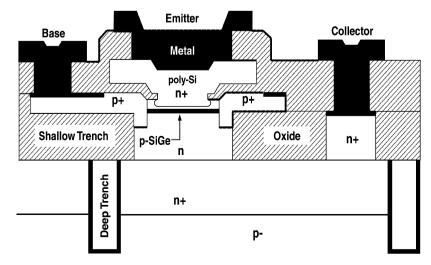

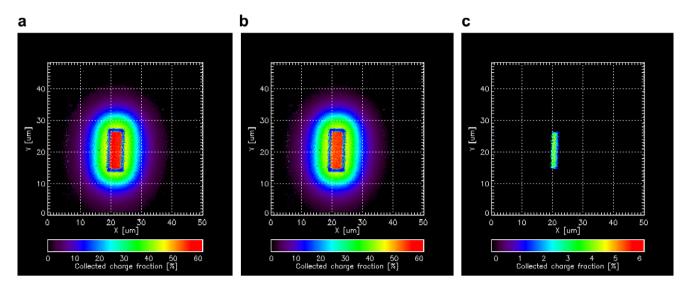

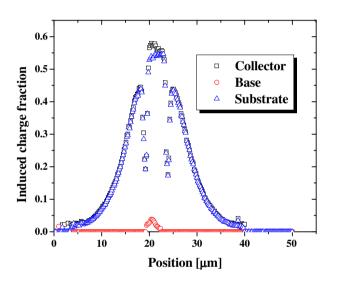

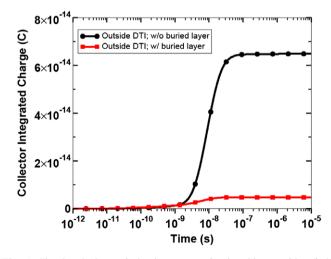

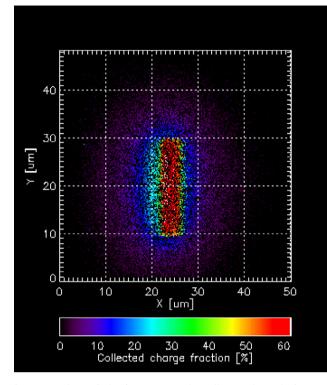

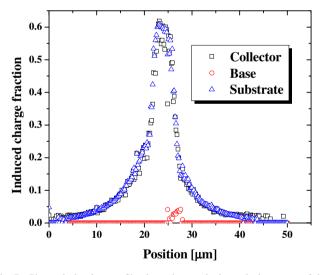

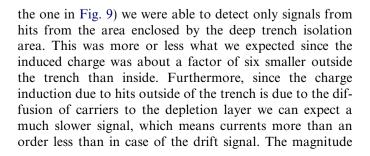

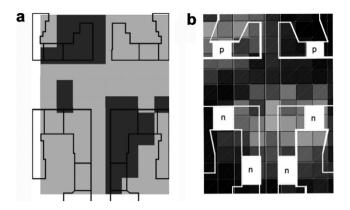

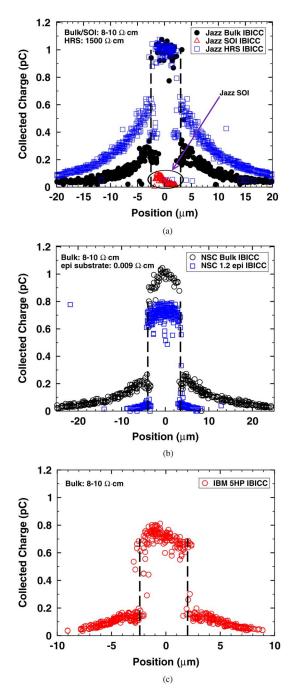

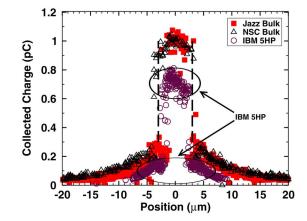

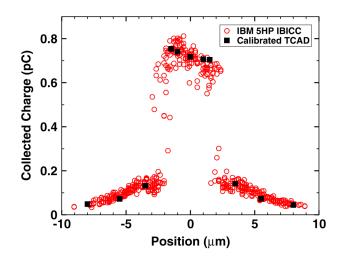

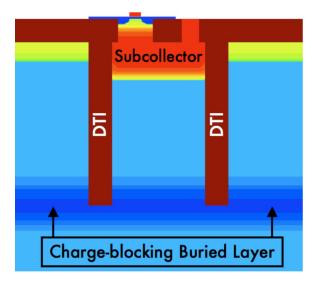

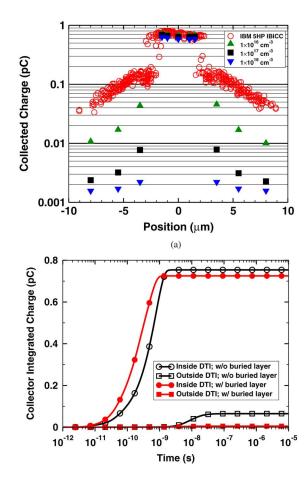

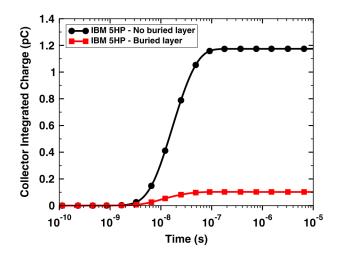

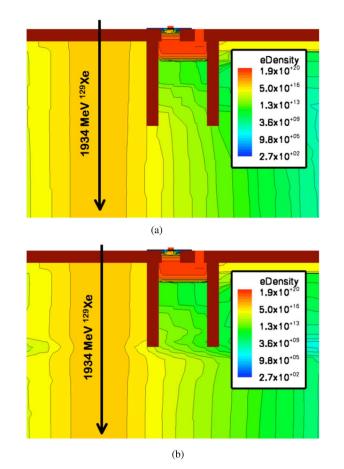

- [5] J. A. Pellish, R. A. Reed, R. D. Schrimpf, M. L. Alles, M. Varadharajaperumal, G. Niu, A. K. Sutton, R. M. Diestelhorst, G. Espinel, R. Krithivasan, J. P. Comeau, J. D. Cressler, G. Vizkelethy, P. W. Marshall, R. A. Weller, M. H. Mendenhall, and E. J. Montes, "Substrate Engineering Concepts to Mitigate Charge

Collection in Deep Trench Isolation Technologies," IEEE Trans. Nucl. Sci., vol. 53, no. 6, pp. 3298-3305, 2006.

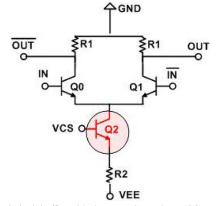

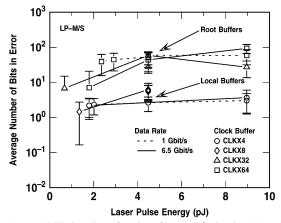

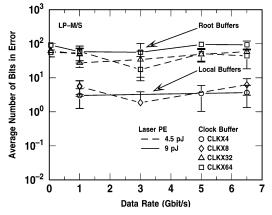

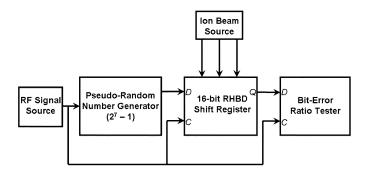

- [6] A. K. Sutton, R. Krithivasan, P. W. Marshall, M. A. Carts, C. Seidleck, R. Ladbury, J. D. Cressler, C. J. Marshall, S. Currie, R. A. Reed, G. Niu, B. Randall, K. Fritz, D. McMorrow, and B. Gilbert, "SEU Error Signature Analysis of Gbit/s SiGe Logic Circuits Using a Pulsed Laser Microprobe," IEEE Trans. Nucl. Sci., vol. 53, no. 6, pp. 3277 3284, 2006.

- [7] R. Krithivasan, P. W. Marshall, M. Nayeem, A. K. Sutton, W. M. Kuo, B. M. Haugerud, L. Najafizadeh, J. D. Cressler, M. A. Carts, C. J. Marshall, D. L. Hansen, K. C. M. Jobe, A. L. McKay, G. Niu, R. Reed, B. A. Randall, C. A. Burfield, M. D. Lindberg, B. K. Gilbert, E. S. Daniel, "Application of RHBD Techniques to SEU Hardening of Third-Generation SiGe HBT Logic Circuits," IEEE Trans. Nucl. Sci., vol. 53, pp. 3400 3407, no. 6, 2006.

- [8] E. J. Montes, R. A. Reed, J. A. Pellish, M. L. Alles, R. D. Schrimpf, R. A. Weller, M. Varadharajaperumal, G. Niu, A. K. Sutton, R. Diestelhorst, G. Espinel, R. Krithivasan, J. P. Comeau, J. D. Cressler, P. W. Marshall, and G. Vizkelethy, "Single Event Upset Mechanisms for Low-Energy-Deposition Events in SiGe HBTs," accepted for publication in IEEE Trans. Nucl. Sci., 2007.

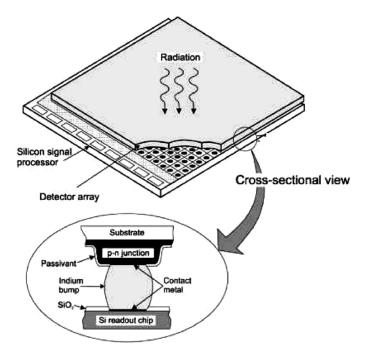

# Task #4. Sensors

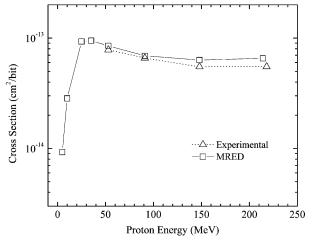

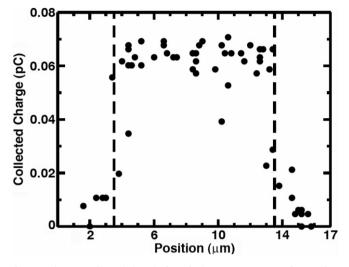

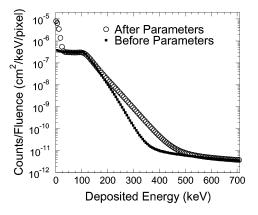

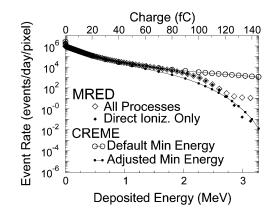

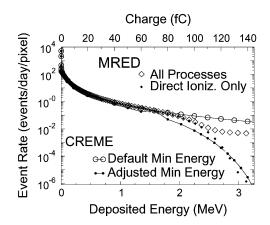

VU/ISDE supported NASA/GSFC's investigation of radiation effects in imagers by performing detail radiation transport simulation using our MRED tool. These results were used to support analysis of transient effects in Si P-I-N diode array (testing performed by AFRL with NEPP/DTRA support)

This past two years we complete the following research:

• Analysis of transient effects in Si P-I-N diode array

Technical Reports and Presentations:

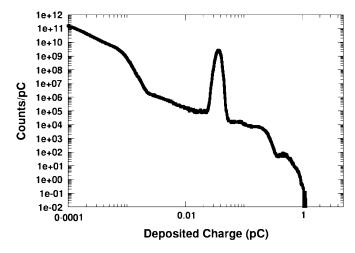

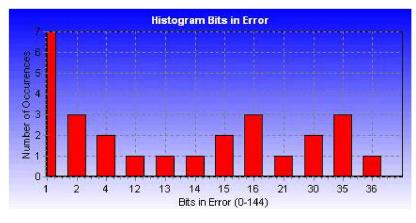

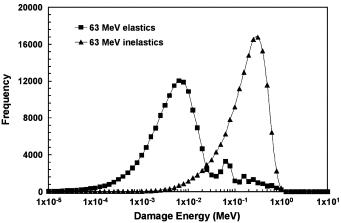

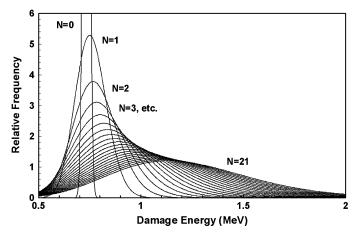

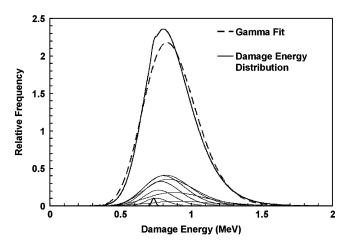

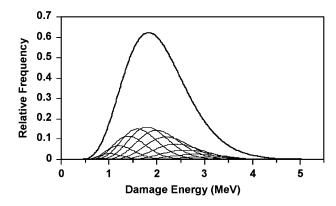

- C. L. Howe, R. A. Weller, R. A. Reed, B. D. Sierawski, P. W. Marshall, C. J. Marshall, M. H. Mendenhall, R. D. Schrimpf, J. E. Hubbs, "Distribution of Proton-Induced Transients in Silicon Focal Plane Arrays," IEEE Trans. Nuc. Sci., vol. 54, no. 6, pp. 2444 - 2449, 2007.

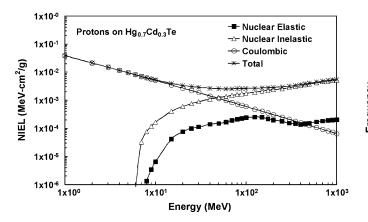

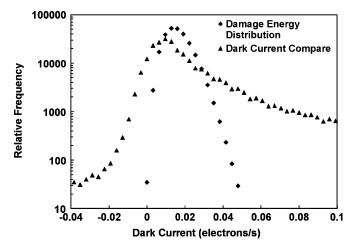

- C. J. Marshall, P. W. Marshall, C. L. Howe, R. A. Reed, R. A. Weller, M. Mendenhall, A. Waczynski, R. Ladbury, and T. M. Jordan, "Comparison of Measured Leakage Current Distributions with Calculated Damage Energy Distributions in HgCdTe," IEEE Trans. Nuc. Sci., vol. 54, no. 4, pp. 898 903, 2007.

# Task #1: Validation of Geant 4 Radiation Transport Model for Space Applications CMOS – related articles.

# Impact of Ion Energy and Species on Single Event Effects Analysis

R. A. Reed, Member, IEEE, R. A. Weller, Senior Member, IEEE, M. H. Mendenhall,

J.-M. Lauenstein, Student Member, IEEE, K. M. Warren, J. A. Pellish, Student Member, IEEE,

R. D. Schrimpf, Fellow, IEEE, B. D. Sierawski, Member, IEEE, L. W. Massengill, Fellow, IEEE,

P. E. Dodd, Senior Member, IEEE, M. R. Shaneyfelt, Fellow, IEEE, J. A. Felix, Member, IEEE,

J. R. Schwank, Fellow, IEEE, N. F. Haddad, R. K. Lawrence, J. H. Bowman, and R. Conde

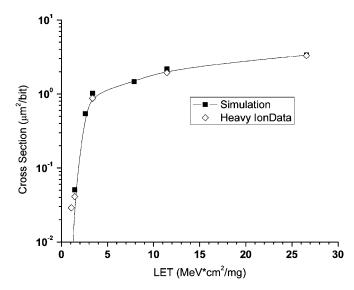

Abstract—Experimental evidence and Monte-Carlo simulations for several technologies show that accurate SEE response predictions depend on a detailed description of the variability of radiation events (e.g., nuclear reactions), as opposed to the classical singlevalued LET parameter. Rate predictions conducted with this simulation framework exhibit excellent agreement with the average observed SEU rate on NASA's MESSENGER mission to Mercury, while a prediction from the traditional IRPP method, which does not include the contribution from ion-ion reactions, falls well below the observed rate. While rate predictions depend on availability of technology information, the approach described here is sufficiently flexible that reasonably accurate results describing the response to irradiation can be obtained even in the absence of detailed information about the device geometry and fabrication process.

*Index Terms*—Nuclear reactions, single event effects (SEE), single event effect rate.

## I. INTRODUCTION

**S** INGLE event effects (SEE) analysis techniques akin to the rectangular parallelepiped (RPP) model [1] have been shown to provide accurate reliability/survivability estimates for single event upsets (SEUs) in certain technologies, while for other technologies and effects the model has been shown to be inadequate. Specifically, the applicability of linear energy transfer (LET) as an engineering metric has been questioned for many years ([2]–[10] and references within). Until recently,

Manuscript received July 20, 2007; revised October 2, 2007. This work was supported in part by the NASA Electronic Parts and Packaging Program and the Defense Threat Reduction Agency Radiation Hardened Microelectronics Program. The portion of this work performed at Sandia was supported by the U.S. Department of Energy. Sandia is a multiprogram laboratory operated by Sandia Corporation, a Lockheed Martin Company, for the U.S. Department of Energy's National Nuclear Security Administration under Contract DE-AC04-94AL85000.

R. A. Reed, R. A. Weller, J. A. Pellish, R. D. Schrimpf, and L. W. Massengill are with the Department of Electrical Engineering and Computer Science, Vanderbilt University, Nashville, TN 37235 USA (e-mail: robert.reed@vanderbilt.edu).

M. H. Mendenhall is with the Free Electron Laser, Vanderbilt University, Nashville, TN 37235 USA.

J.-M. Lauenstein is with NASA GSFC, Greenbelt, MD 20771 USA.

K. M. Warren and B. D. Sierawski are with the Institute for Space and Defense Electronics, Vanderbilt University, Nashville, TN 37203 USA.

P. E. Dodd, M. R. Shaneyfelt, J. A. Felix, and J. R. Schwank are with Sandia National Laboratories, Albuquerque, NM 87185 USA.

N. F. Haddad, R. K. Lawrence, and J. H. Bowman are with BAE Systems, Manassas, VA 20110 USA.

R. Conde is with the Applied Physics Laboratory, Johns Hopkins University, Laurel, MD 20723 USA.

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TNS.2007.909901

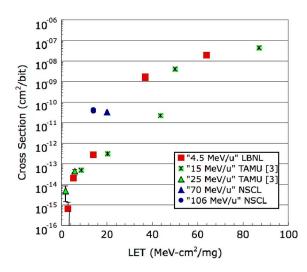

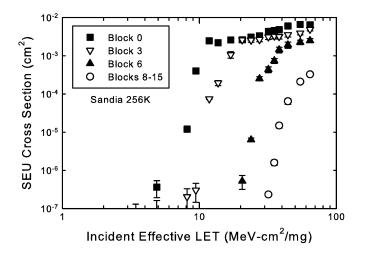

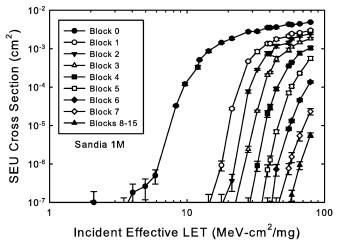

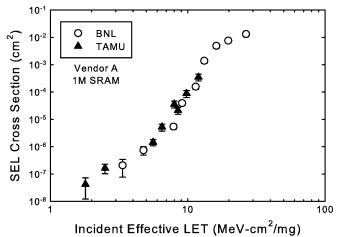

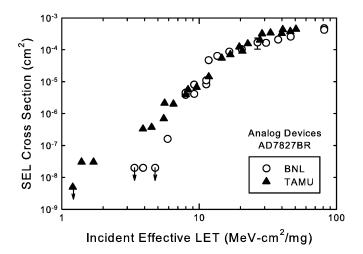

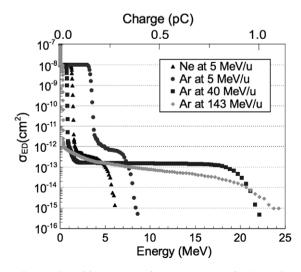

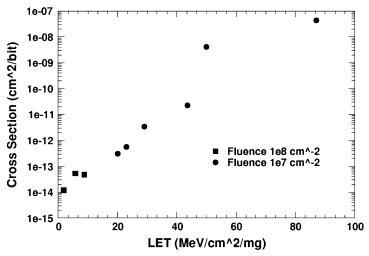

Fig. 1. Measured SEU cross section versus LET of normal incident ions at several different facilities. The data show two orders of magnitude difference at a fixed LET, depending on the ion specie and energy used for testing.

careful analysis of experiments has shown that, for the most part, these concerns could be resolved by modifying the RPP model while maintaining use of the concepts of effective LET and effective SEU cross section (in this paper we make a careful distinction between effective LET and effective cross section, as defined in [1], and the actual ion LET and measured SEU cross section without correction for incident angle).

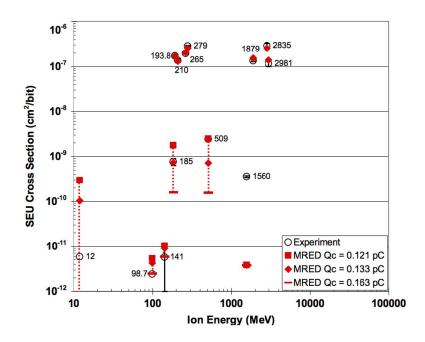

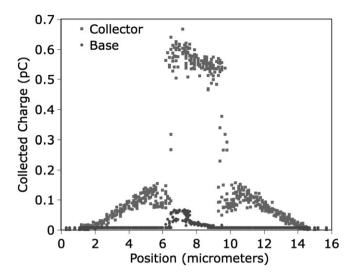

Fig. 1 displays SEU data taken on modern high-reliability, radiation-hardened SRAMs (described in [3]—in this paper we will call this "SRAM#1"). The data were taken at three different facilities, for a range of ion energies, and all ions were normally incident (we will look more closely at these data in the next section). The key point, for now, is the lack of correlation between the measured SEU cross section and ion LET; in particular, notice the large inconsistencies in the data near 14, 20, and 40 MeV-cm<sup>2</sup>/mg—note that this is not due to anomalies that result from the concepts of effective LET and SEU cross section. In [4] and [5], Dodd et al. presented data showing a poor correlation of effective SEU and single event latchup (SEL) cross sections with effective LET for several SRAMs. It is impossible to use data in which there is a lack of correlation of the SEE cross section with ion LET to make reliable predictions of on-orbit SEU rates using techniques based on integral RPP (IRPP) methods.

In [3] simulations were used to predict the SEU cross section dependence on ion energy and species, as distinguished from LET, when nuclear reactions dominate the response. In [6] nuclear reactions were shown to contribute to heavy ion cross sections in commercial memories using low LET C ions. Nuclear reactions have also been considered in evaluating low threshold, low probability upsets in memories as a function of ion energy in [7]. The authors of [8] base their analysis of SEUs in a radiation hardened SRAM on the fact that products from Coulomb scattering events could simultaneously hit two nodes. This SRAM used an SEU mitigation scheme that requires charge collection at more than one node to upset the memory cell. Other studies have questioned the applicability of LET as a ground test metric for SEE because of the difference in the ionized electron structure of the track [9], [10].

There is mounting evidence that ion LET (particularly effective LET) is not an appropriate metric to describe the SEE response of many of today's advanced technologies. We have published several papers [2], [3], [11]–[21] that use a new approach to deal with this issue that is based on a collection of software tools that use physically based models to describe the radiation transport and event generation, and predict the device/circuit response. A key component of this technique is the MRED (Monte Carlo radiative energy deposition) simulation tool. MRED is based on Geant4 [22], which is comprised of the best available computational physics models for the transport of radiation through matter. Geant4 is a library of c++ routines for describing radiation interaction with matter assembled by a large and diverse international collaboration. MRED includes a model for screened Coulomb scattering of ions, tetrahedral geometric objects, a cross section biasing and track weighting technique for variance reduction, and a number of additional features relevant to semiconductor device applications. The Geant4 libraries contain alternative models for many physical processes, which differ in levels of detail and accuracy. Generally, MRED is structured so that all physics relevant for radiation effects applications are available and selectable at run time.

In [2], [3], and [16] it was shown that the SEU cross section could depend on ion energy and species, rather than just LET, when nuclear reactions dominate the response. In [3] we used similar arguments to suggest that the low LET upsets in Fig. 1 (collected at Texas A&M University-TAMU) were due to nuclear reactions. However, these studies lacked experimental data over a range of ion energies and species to confirm the theory. Also, the results of [3] do not address the issue of whether the nuclear reaction contribution significantly impacts the observed on-orbit event rate.

In this paper, new ground and space based experimental results and new MRED simulation results for several technologies show that accurate SEE response predictions depend on a detailed description of the variability of radiation events (e.g., nuclear reactions) as opposed to the classical single-valued LET parameter. The MRED-based event rate prediction method provided in [2] is updated based on these new results. The rate-prediction method is validated by showing excellent agreement with the average observed SEU rate on NASA's Mercury Surface, Space Environment, Geochemistry, and Ranging (MESSENGER) mission to Mercury. In contrast, a prediction based on the traditional IRPP method, which does not include the contribution from ion-ion reactions, falls well below the observed rate.

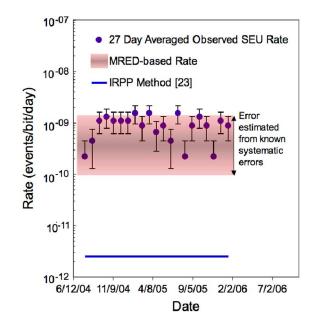

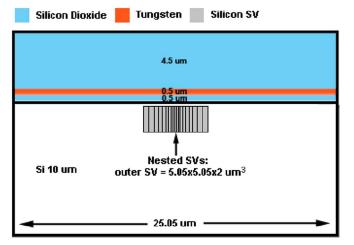

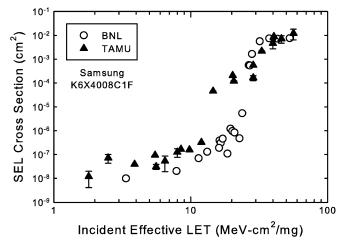

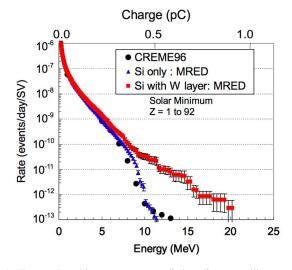

Fig. 2. Comparison of the MRED based event rate predictions for SRAM#1 to measured data on a NASA mission. Also plotted is the predict rate using IRPP [23]. We assumed 100 mils of Al shielding.

### II. SEUS IN HIGH CRITICAL CHARGE SRAMS

## A. On-Orbit SEU Rates (Observation and Modeling)

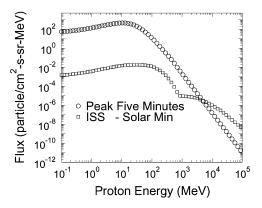

NASA's MESSENGER mission uses 40 SRAM#1s; measured on-orbit SEU data for these parts were provided by Johns Hopkins APL. Fig. 2 shows a plot of the 27-day averaged rate for SEUs observed on MESSENGER (the data points are represented by filled circles and one-sigma counting statistics error bars are included). This figure also shows predictions from MRED (including estimated error) and the Integral RPP method [23]. The measured 27-day averaged SEU on-orbit rate is between  $2.2 \times 10^{-10}$  and  $1.5 \times 10^{-9}$  errors/bit/day.

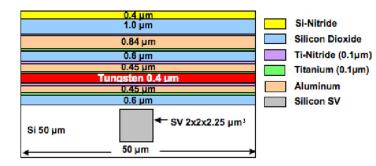

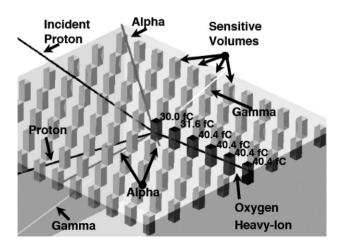

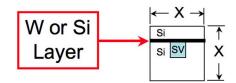

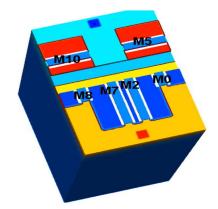

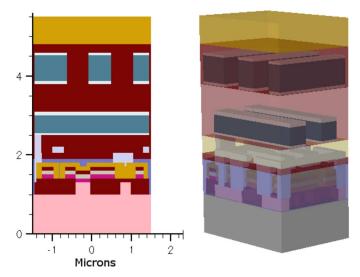

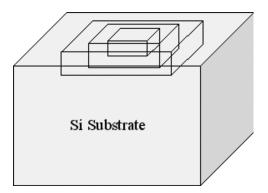

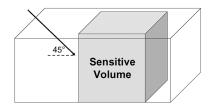

MRED was used to compute the SEU event rate for depositing energy in the sensitive volume for the solar-quiet/solar minimum galactic cosmic ray background (see Section IV for a complete description of the rate prediction method). In [3] we determine the sensitive volume geometry for this SRAM#1 to be  $2 \times 2 \times .25 \ \mu m^3$ . The surrounding material in the simulations is consistent with the overlayers used to fabricate the SRAM (Fig. 3). The environment was predicted using the models on the CREME96 website [24]. Computations from MRED predict an event rate between  $8.6 \times 10^{-11}$  and  $8.6 \times 10^{-9}$  errors/bit/day. The upper and lower values were determined from the fit of the MRED results to data in Fig. 1 (see Section II-C), and are a result of the systematic uncertainty in Geant4 nuclear physics (see the Appendix) and the limited description of the sensitive volume and the overlayers.

The MRED prediction of the SEU rate is in excellent agreement with the average observed rate on MESSENGER. However, using the traditional IRPP approach for rate prediction yields a rate of  $2.5 \times 10^{-12}$  errors/bit/day, a factor of 88 to 618 lower than the rate observed on MESSENGER.

LET is defined as the mean energy lost by an ion per unit path length in collisions with electrons of the material, and is

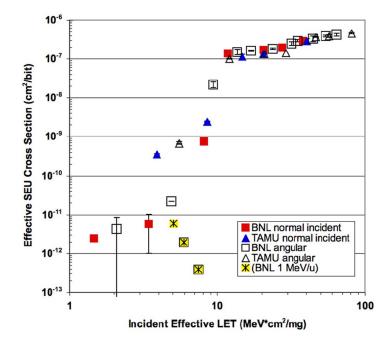

Fig. 3. Sensitive volume and overlayer used for MRED simulation of SRAM#1. The volume thickness is  $2.25 \,\mu$  m. The sensitive volume geometry was determined in [3] using TCAD. While MRED events can be coupled directly to TCAD [15], [18], the simulation approach used in this work was to tabulate energy deposited the sensitive volume.

| Test<br>Facility         Species-<br>Atomic Mass         Energy<br>(MeV)         LET<br>(MeV-cm <sup>2</sup> /mg)         Computation Meth<br>(MeV-cm <sup>2</sup> /mg)           LBNL         N-15         68         2.9         Full           LBNL         Ne-20         90         5.3         Full           LBNL         Ne-20         90         5.3         Full           LBNL         Ar-40         180         14         Full           LBNL         Kr-86         387         37         Full           LBNL         Xe-136         612         64         No Nuclear Reaction           TAMU         Ne-22*         523         1.8         Full           TAMU         Ar-40*         494         8.7         Full           TAMU         Ar-40*         919         5.8         Full           TAMU         Ag-109*         1200         44         No Nuclear Reaction |        |         |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|---------|

| LBNL         N-15         68         2.9         Full           LBNL         Ne-20         90         5.3         Full           LBNL         Ar-40         180         14         Full           LBNL         Ar-40         180         14         Full           LBNL         Kr-86         387         37         Full           LBNL         Ke-136         612         64         No Nuclear Reaction           TAMU         Ne-22*         523         1.8         Full           TAMU         Ar-40*         494         8.7         Full           TAMU         Ar-40*         919         5.8         Full           TAMU         Ag-109*         1200         44         No Nuclear Reaction                                                                                                                                                                                   | `est   | Test    |

| LBNL         Ne-20         90         5.3         Full           LBNL         Ar-40         180         14         Full           LBNL         Kr-86         387         37         Full           LBNL         Kr-86         387         37         Full           LBNL         Xe-136         612         64         No Nuclear Reaction           TAMU         Ne-22*         523         1.8         Full           TAMU         Ar-40*         494         8.7         Full           TAMU         Ar-40*         919         5.8         Full           TAMU         Ag-109*         1200         44         No Nuclear Reaction                                                                                                                                                                                                                                                   | cility | Facilit |

| LBNL         Ar-40         180         14         Full           LBNL         Kr-86         387         37         Full           LBNL         Xe-136         612         64         No Nuclear Reaction           TAMU         Ne-22*         523         1.8         Full           TAMU         Ar-40*         494         8.7         Full           TAMU         Ar-40*         919         5.8         Full           TAMU         Ag-109*         1200         44         No Nuclear Reaction                                                                                                                                                                                                                                                                                                                                                                                     | BNL    | LBNI    |

| LBNL         Kr-86         387         37         Full           LBNL         Xe-136         612         64         No Nuclear Reaction           TAMU         Ne-22*         523         1.8         Full           TAMU         Ar-40*         494         8.7         Full           TAMU         Ar-40*         919         5.8         Full           TAMU         Ag-109*         1200         44         No Nuclear Reaction                                                                                                                                                                                                                                                                                                                                                                                                                                                      | BNL    | LBNI    |

| LBNL         Xe-136         612         64         No Nuclear Reaction           TAMU         Ne-22*         523         1.8         Full           TAMU         Ar-40*         494         8.7         Full           TAMU         Ar-40*         919         5.8         Full           TAMU         Ag-109*         1200         44         No Nuclear Reaction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | BNL    | LBNI    |

| TAMU         Ne-22*         523         1.8         Full           TAMU         Ar-40*         494         8.7         Full           TAMU         Ar-40*         919         5.8         Full           TAMU         Ag-109*         1200         44         No Nuclear Reaction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | BNL    | LBNI    |

| TAMU         Ar-40*         494         8.7         Full           TAMU         Ar-40*         919         5.8         Full           TAMU         Ag-109*         1200         44         No Nuclear Reaction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | BNL    | LBNI    |

| TAMU         Ar-40*         919         5.8         Full           TAMU         Ag-109*         1200         44         No Nuclear Reaction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | MU     | TAMI    |

| TAMU Ag-109* 1200 44 No Nuclear Reaction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | MU     | TAMI    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | MU     | TAMI    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | MU     | TAMI    |

| TAMU Au-197* 2000 87 No Nuclear Reaction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | MU     | TAMU    |

| TAMU Cu-63* 729 20 Full                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | MU     | TAMI    |

| TAMU Ag-109* 665 50 No Nuclear Reaction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | MU     | TAMI    |

| NSCL Xe-136 14416 14 None                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | SCL    | NSCL    |

| NSCL Xe-136 9520 20 None                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | SCL    | NSCL    |

TABLE I IONS USED FOR TESTING SRAM#1

\* From [3]

a good quantity to characterize the energy available to produce ionization (free charge). Ionization from the primary particle is called direct ionization. Indirect ionization, induced by secondary particles from ion-ion reactions, can result in large amounts of localized energy deposited near SEE sensitive structures.

The SEU rate includes contributions from three interaction processes between the ion and the target semiconductor: 1) direct ionization induced by the primary ions, 2) indirect ionization via atomic displacements caused by Coulomb scattering between target atoms and the incident ion, and 3) indirect ionization from nuclear reaction products involving the incident ion and the target nucleus. The relative contribution of each mechanism to the overall rate depends on the number of sensitive volumes, cell critical charge, amount and location of high-Z materials, and the ion species, energy, and fluence used in the testing [2], [3], [17], [19].

To compute an event rate for the environment considered here, MRED fully simulates each of the processes defined above for an ensemble of omnidirectionally incident primary particles, applies the appropriate interaction cross sections, and records the energy loss of the primary particle and all secondary particles within a defined box (called the sensitive volume).

The traditional rate-estimation methods, like IRPP, do not include the variability of radiation events (e.g., nuclear reactions). Instead they approximate the direct ionization by assuming a single (often constant) value for the LET parameter. These older models do not include energy deposition from indirect ionization events. The MRED-calculated rate is in much better agreement with the observed on-orbit rate than that predicted by the classical method.

# B. SEUs at Heavy Ion Accelerator Facilities

New SEU cross section data were collected on two radiation hardened SRAMs (called SRAM#1 and SRAM#2) at two SEE test facilities: Lawrence Berkeley National Laboratory (LNBL), and the National Superconducting Cyclotron Laboratory (NSCL). The ions used are listed in Table I. The ion energy and associated LET are also listed in Table I. Fig. 1 compares these data taken on SRAM#1 to the data given in [3]. (The details of the test setup are identical to those described in [3]). Error bars representing two standard deviations (98% confidence interval) are included; the symbols hide the error bars for the cases where they cannot be seen.

The intent of this testing was to determine the dependence of the measured SEU cross section on incident ion energy and species for normally incident ions. As stated in the introduction, the inconsistencies at several values of LET clearly show that direct ionization from the primary particle (or LET) cannot be used to describe the trends in the data completely. For example, comparing the measured cross section for ions that have a LET of 14 MeV  $\cdot$  cm<sup>2</sup>/mg, we see that the cross section using the 14.4 GeV Xe ions at NSCL (filled circle) is two orders of magnitude higher than that measured with the 180 MeV Ar ions at LBNL (filled square), although both particles have the same LET. The high atomic mass (A), high-energy ion produces a higher SEU cross section than the low A, low-energy ion. The same can be said for ions with LETs of 20 MeV  $\cdot$  cm<sup>2</sup>/mg (9.25 GeV Xe ions and the 729 MeV Cu ions). However, comparing data near an LET of 40 MeV-cm<sup>2</sup>/mg shows that using the low A, low-energy ion produced a higher SEU cross section than that with the high A, high-energy ion. Notice that the inconsistencies in the data disappear at high LET and at low LET. There appears to be no simple predictable trend with ion LET (even ionization track radius), species, and/or ion energy!

Finally, we note that at high LET values, where the cross section is near  $4 \times 10^{-8}$  cm<sup>2</sup>, direct ionization dominates the response. At these LET values, the LBNL and TAMU results agree and are consistent with the expected sensitive volume geometry as measured by laser testing and as determined via TCAD [3]. We also note that [25] provides data that show that the dosimetry at NSCL is consistent with other radiation effects test facilities, so the trends in the data are physically meaningful and not artifacts induced by facility differences.

Similar trends in the measured cross section were observed for SRAM#2 using ions that have an LET of 14 MeV-cm<sup>2</sup>/mg. The measured cross section at 14.4 GeV Xe ions at NSCL is  $1.4 \times 10^{-11}$  cm<sup>2</sup>/bit. The measured value ( $1.4 \times 10^{-13}$  cm<sup>2</sup>/bit) for the 180 MeV Ar ions at LBNL is two orders of magnitude lower than that measured at NSCL. Again, the high *A*, highenergy ion produces a higher SEU cross section than the low *A*, low-energy ion.

In the next section, we show that accurate SEE response predictions depend on a detailed description of the variability of radiation events (e.g., nuclear reactions), as opposed to the classical single-valued LET parameter, in order to explain the data in Fig. 1. MRED, which includes high fidelity physics models for all physical processes, is used for the cross section calculations.

## C. Discussion and Hardness Assurance Issues

To model the ground test environment, MRED fully simulates each of the processes defined in Section II-A for an ensemble of unidirectionally incident primary particles, applies the appropriate interaction cross sections, and records the energy loss of the primary particle and all secondary particles within the sensitive volume (Fig. 3). The cross section for depositing a specific energy, E, or greater is computed [2], [3]. These results are used to determine the SEU cross section by defining a critical charge (equivalently a critical energy) for upset. Conversely, if the measured SEU cross section is known, the critical energy (or critical charge) can be determined. In [3] we TCAD simulation to define ademonstrated the use of MRED to determine the contribution of various energy deposition processes to the SEU cross section.

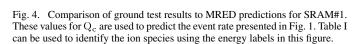

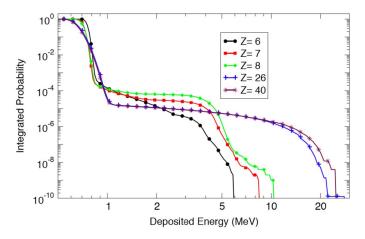

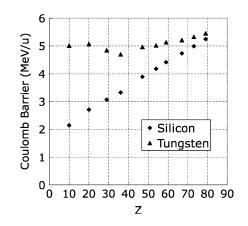

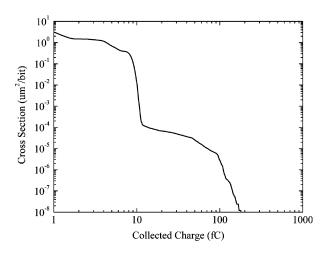

The MRED simulation tool was used to simulate the twelve lowest energy ions listed in Table I. Current limitations within Geant4 (Geant4.8.1.p02) prevent the simulation of nuclear reactions for ions with a large atomic mass (> Z = 36) [2]; therefore, the two ions used at NSCL were not simulated. Fig. 4 shows the measured SEU cross section (data from Fig. 1) for each ion (open circles). The measured data contain error bars

that represent a 95% confidence interval. The figure also shows the fit of MRED results to the measured SEU cross section data (fitting is described in the next few paragraphs). The abscissa is the total ion energy. Each data point is also labeled by the ion energy, which can be used to identify the ion species using Table I. MRED simulations are in good agreement with measured data.

Simulation results can be separated into two categories: SEUs induced by direct ionization and those induced by indirect ionization. The systematic errors described in the Appendix require that each category must be analyzed separately. Geant4 is much more accurate at predicting effects from direct ionization than those from indirect ionization. We determined that the simulation results are dominated by direct ionization effects for the Ar(387 MeV), Kr(665 MeV), Xe(612 MeV), Au(2 GeV), and Ag(1.2 GeV) ions. Indirect ionization effects dominate for all other ions.

The experimental data presented in Fig. 4 were used to determine the best value for critical charge. The value for the critical charge for direct ionization events was determined to be 1.02pC (or 23 MeV), while for indirect ionization the fit to the data resulted in a range from 0.7 to 1.02 pC. This is not a surprising result given that a simple structure was assumed for the sensitive volume (Fig. 3) and that there are known systematic errors in Geant4 (see the Appendix).

We conclude that accurate SEE response predictions depend on a detailed description of the variability of radiation events (i.e., all applicable interaction physics must be used) to describe the data in Fig. 1 fully. We also conclude that tests over energy and species similar to that given in Table I, excluding the high-energy ions at NSLC, are sufficient to provide estimates for error rates. However, the testing at NSCL allowed us to conclude, with certainty, that LET is not the appropriate metric when studying single event upsets in these technologies. Further hardness assurance issues are discussed in [5].

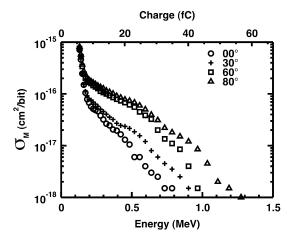

Fig. 5. Measured SEU cross section versus LET of normal and angularly incident ions on SRAM#3 (reproduced from [5]). At LETs less than 10 MeV-cm<sup>2</sup>/mg, cross sections become very dependent on ion species and energy; note that at very low energy, cross section decreases with increasing angle.

TABLE II

IONS USED FOR TESTING SRAM#3 (FROM [5])

| Test     | Species-    | Energy | LET          | Angles    | Computation Method   |

|----------|-------------|--------|--------------|-----------|----------------------|

| Facility | Atomic Mass | (MeV)  | (MeV-cm²/mg) | Tested    |                      |

| BNL      | C-12        | 12     | 1.464        | 0, 30, 45 | Full                 |

| BNL      | C-12        | 98.7   | 5.07         | 0, 45     | Full                 |

| BNL      | F-19        | 141    | 3.428        | 0, 45     | Full                 |

| BNL      | Si-28       | 185    | 8.126        | 0, 30     | Full                 |

| BNL      | Ti-48       | 193.8  | 11.81        | 0, 30     | Full                 |

| BNL      | CI-35       | 210    | 20.54        | 0, 30, 45 | Full                 |

| BNL      | Ni-58       | 265    | 27.49        | 0, 30     | Full                 |

| BNL      | Br-81       | 279    | 38.24        | 0, 30, 45 | Full                 |

| TAMU     | Ar-40       | 509    | 8.55         | 0, 45     | Full                 |

| TAMU     | Ar-40       | 1560   | 3.9          | 0, 45     | Full                 |

| TAMU     | Kr-84       | 1879   | 20.4         | 0, 45     | Full                 |

| TAMU     | Kr-40       | 2981   | 14.7         | 0, 45     | Full                 |

| TAMU     | Xe-136      | 2835   | 40.2         | 0, 30, 45 | No Nuclear Reactions |

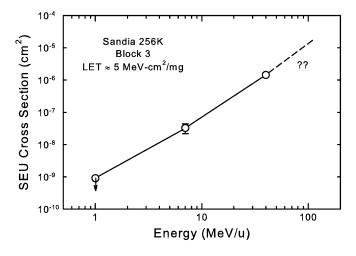

## III. SEUS IN LOW CRITICAL CHARGE SRAMS

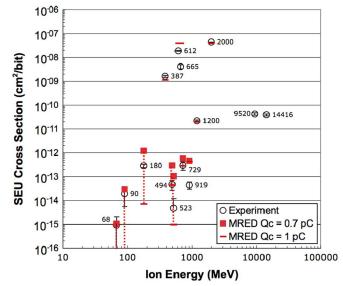

#### A. Experimentally Measured Cross Section

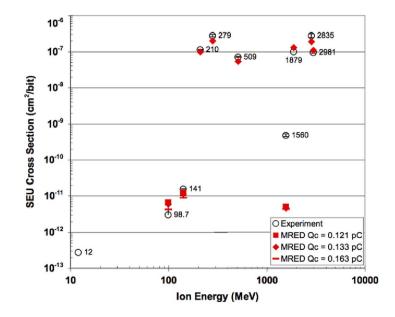

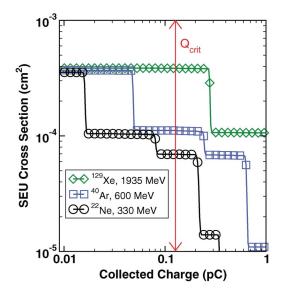

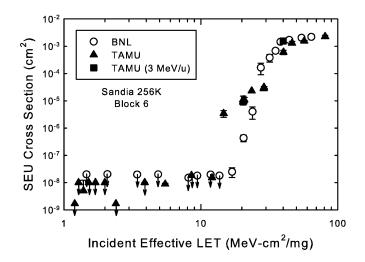

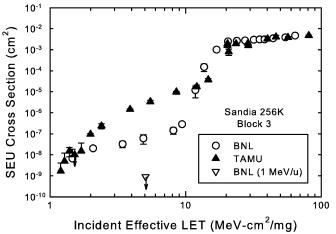

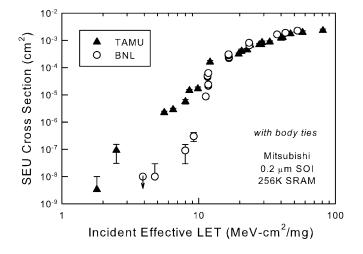

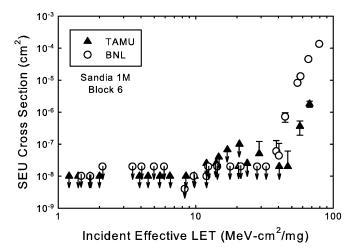

In SRAMs with low critical charge, we expect a reduced role of indirect ionization relative to direct ionization in causing single-event upsets [2], [3]. Examination of test data from [5] for a block of a 0.5- $\mu$ m bulk 256-kbit SRAM without feedback resistors (hereafter referred to as SRAM#3) reveals that the measured SEU cross section for a fixed LET depends on ion energy and species, despite this block having a low critical charge for upset (Fig. 5). Details of the SRAM process and test methods are given in [26] and [5], respectively.

SEU tests on SRAM#3 were conducted at Brookhaven National Laboratory (BNL) and TAMU. Table II lists the ions used, their energies, and effective LETs. It is not the intent here to discuss these results in detail; this discussion can be found in [5]. The key point is that once again, there is no simple relationship between SEU cross section and ion LET.

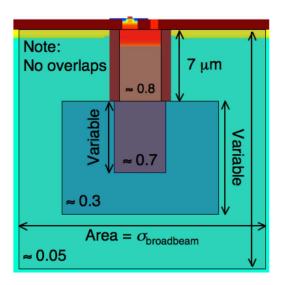

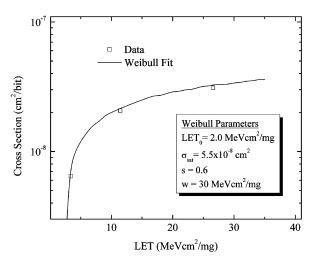

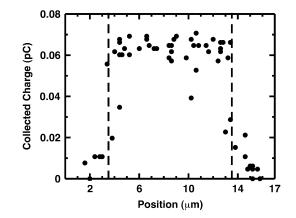

# B. Simulation of the SRAM#3 Measured SEU Cross Section

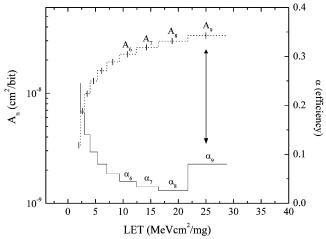

MRED was used to predict energy deposition distributions in a carefully selected sensitive volume for all ions listed in Table II. The method defined in [12] was used to develop the sensitive volume, which is to construct a concentric set of charge collection regions with different collection efficiencies by assuming a threshold LET of 7.5 MeV-cm<sup>2</sup>/mg for upsets induced by direct ionization. The normally incident BNL data in Fig. 5 for this LET and higher were used to construct a set of ten weighted, concentrically nested sensitive regions; the aggregate of these regions defines the sensitive volume. Following the method detailed in [12], cross sections at each of ten logarithmically uniform points along the upset curve from 7.5 to 38 MeV-cm<sup>2</sup>/mg were used to define the areas of the sensitive volumes. All of these regions have depths of 2  $\mu$ m. Charge collection efficiencies were assigned per [12] such that all efficiencies summed to 100% in the center region where the ten volumes overlap. No assumptions were made as to the composition of the

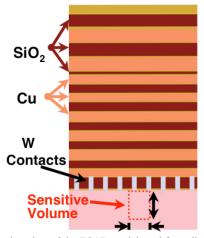

Fig. 6. Sensitive volumes and overlayers used for simulation of SRAM#3.

overlayers; the tungsten vias were modeled as a 0.5  $\mu$ m layer placed 0.5  $\mu$ m above the base of a 5.5  $\mu$ m silicon-dioxide overlayer (Fig. 6). This simulation configuration was done without any process, circuit or device information.

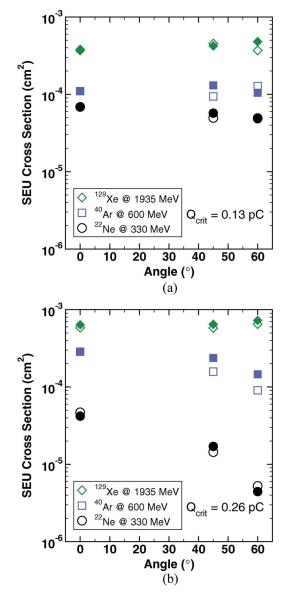

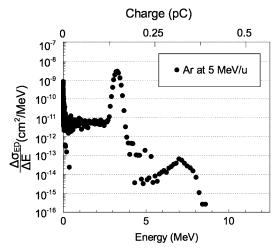

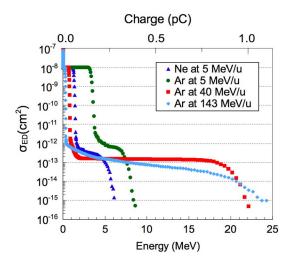

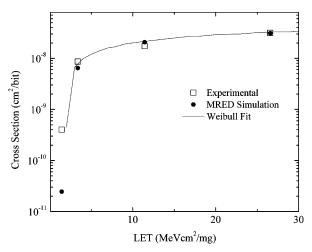

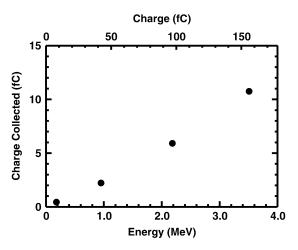

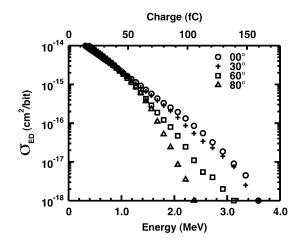

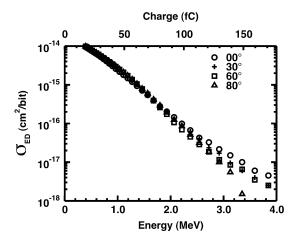

Simulation results fitted to measured data are shown in Fig. 7 for incident ions normal to the die surface. Non-zero upset cross sections for C(98.7 MeV), F(141 MeV), and Ar(1560 MeV) are due to indirect ionization effects. MRED revealed that C(12 MeV), Si(185 MeV) and Ar(509 MeV) ions are in the threshold region [3] for causing upset due to direct ionization, with indirect ionization from Coulomb scattering potentially contributing to the cross section as well. Direct ionization effects dominate for all other ions. Using the fitting method described earlier, the critical charge for direct ionization events was determined to be 0.133 pC (or 3 MeV). As can be seen for the C(98.7 MeV) and F(141 MeV) ions, this critical charge fits these low-energy, nuclear-reaction-dominated simulations to the experimental data very well. Incorporation of a fitting range of 0.121 to 0.163 pC improved the fit, bringing the simulations into agreement with experiment for the C(12 MeV) and Ar(509 MeV) simulated ions. Note that the high energy Ar(1560 MeV) cross section remains fixed across this range of critical charge, and is due only to indirectly ionizing effects; the present limitations of Geant4 (see Appendix) prevent an accurate fit to the measured cross section for this high energy ion.

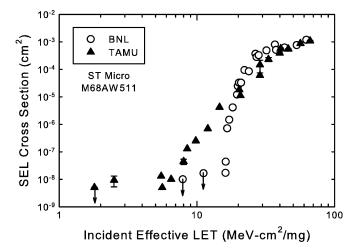

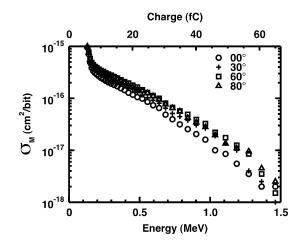

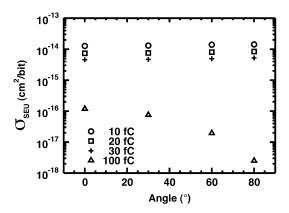

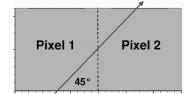

Using the upper and lower limits for critical charge, determined by fitting the normally incident-ion data, MRED simulations reproduce the angle dependence for the SEU response without any adjustable parameters. Simulation and experimental results for  $30^{\circ}$  (not shown) and  $45^{\circ}$  (Fig. 8) angles of incidence are in excellent agreement with measurement. Unlike in Fig. 5, measured data are shown without standard corrections to the fluence for offnormal angles imposed by the RPP method, i.e., the SEU cross sections are not effective cross sections. At both  $30^{\circ}$  and  $45^{\circ}$  angles, C(12 MeV) has a diminished measured cross section as compared with  $90^{\circ}$  incidence. MRED simulated this trend, predicting no upsets at off-normal angles of incidence for the above critical charges. This underprediction could be due to the very simplified geometry and the chosen sensitive volume depth.

We note that this analysis was done without detailed information about the circuit, device geometry and process. The quality and accuracy of these predictions are directly related to the details of device and circuit structure that are available. However, as the results reported here demonstrate, even relatively crude approximations are often sufficient to produce reasonably accurate simulations that describe responses to irradiation. By including detailed descriptions of all physical processes it has been possible to capture the complex cross section curve of Fig. 5, and to establish a self-consistent data set whose details are explicable in terms of the interaction mechanisms linking the incident ion and the target device.

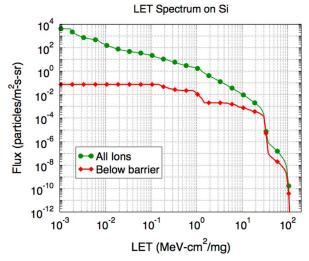

#### IV. SEE RATE PREDICTION METHODOLOGY

In the previous sections we have shown that the variability of radiation events arising from the intrinsic randomness of the physical processes through which radiation interacts with matter now dominate single event effects in multiple technologies. In this section, we show how this variability may be quantified and used to predict the rate of single event effects in devices. The key strategy is Monte Carlo simulation to compute energy depositions in define sensitive volumes.

A Monte Carlo simulation program, such as MRED, may be viewed as a machine for determining a probability distribution by repetitive sampling. It is particularly useful when direct analytical computation of the distribution is difficult or impossible. For example, one might pose the question: "What is the probability density for an isotropic, mono-energetic flux of ions with atomic number Z and energy  $E_0$  to deposit energy E in a specific sensitive volume?" To answer this, MRED computes the energy deposited by a large number of ions with randomly chosen initial trajectories, produces a histogram of the resulting values, normalizes the histogram to unit area, and scales by the width of the histogram bins, to obtain a discrete approximation to a continuous probability density. Subsequently, we will represent this continuous probability density as MRED<sub>z</sub>( $E_0, E$ ).

In order to understand the full Monte Carlo solution for an event rate in the space environment, one must first understand how the function  $MRED_z(E_0, E)$  would be used in an analytic computation to infer the event rate from a knowledge of the flux distribution of the various ions. Let  $\Phi_z(E_0)$  be the flux of ions with atomic number Z and energy  $E_0$ , in units, e.g., of particles/cm<sup>2</sup>/second/ sterradian/MeV. For our computations, these values were obtained from CREME96 by appropriate scaling of the original distributions, which are normalized to energy per nucleon. In the simplest computation, one would integrate the product of  $\Phi$  and  $MRED_z(E_0, E)$  over all energies and scale appropriately by the sample area. However, this presents a challenge for a Monte Carlo computation, due to the very large dynamic range of the flux,  $\Phi$ . To deal with this, it is useful to define a new integration variable r that may be thought of as a random number generated in the usual way in the interval [0], [1]. A function  $E_0(r)$  is chosen that maps each r into an ion energy  $E_0$  in a way that distributes randomly selected energy values to give good sampling statistics in all regions of the flux distribution. In this way, very rare, high-energy ions are simulated as frequently as much more numerous low-energy ions. For this work we chose  $E_0(r) =$  $E_{\min}(E_{\max}/E_{\min})^r$ , where  $[E_{\min}, E_{\max}]$  is the range of CREME96 flux data used. The upper limiting ion energy was chosen to be 20 GeV/nucleon after tests demonstrated that energies above 20 GeV/nucleon did not contribute significantly to

Fig. 7. Comparison of ground test results to MRED predictions for normally incident ions. These values for  $Q_c$  are used to predict the angle dependence in shown in Fig. 8. Table II can be used to identify the ion species using the energy labels in this figure.

Fig. 8. Comparison show very good agreement between ground test results and MRED predictions for ions incident at tilt =  $45^{\circ}$ . The angle of incident was the only simulation parameter that was changed.

final results. The inverse derivative  $n(E_0) \equiv dr/dE_0$  may be thought of as the density of samples at energy  $E_0$  and is uniform on a log scale between  $E_{\min}$  and  $E_{\max}$  for the particular  $E_o(r)$ defined above. This results in a full equation for the differential event rate of

$$\frac{dR(E)}{dE} = \sum_{z=1}^{92} \left( 4\pi^2 \rho^2 \int_0^1 dr \left( \frac{\Phi_z(E_o(r))}{n(E_o(r))} \right) \right.$$

$$\cdot \text{MRED}_z(E_o(r), E) \right). \quad (1)$$

Here  $\pi \rho^2$  is the sample area and a factor of  $4 \pi$  sterradians is included because  $\Phi$  is isotropic and normalized to solid angle. The sum is carried out over all species in the space environment for which CREME96 has data.

Examining (1) it is clear that the r integral can also be evaluated by other numerical techniques. As described above, the set of r values used to evaluate the integral consists of random points that are statistically uniform in the interval [0], [1]. Alternatively, these values may be deterministically uniform. If rvalues are chosen in this way, the difference is simply the difference in integrating by the trapezoid rule or by Monte Carlo integration, and (1) can be recast as follows:

$$\frac{dR(E)}{dE} = \sum_{z=1}^{92} \left( \frac{4\pi^2 \rho^2}{N_z} \sum_{i=1}^{N_z} \left( \frac{\Phi_z(E_o(r_i))}{n(E_o(r_i))} \right) \right)$$

$$\cdot \text{MRED}_z(E_o(r_i), E) \right) \quad (2)$$

where

$$r_i = \frac{2i+1}{2N_z} \approx \frac{i}{N_z}, i = 0, \dots, N_z - 1.$$

(3)

It is evident in (2) that the number of points chosen to evaluate the sum over i can be different for each ion species in the environment, where species is indexed by atomic number Z. In order to maximize the efficiency of the numerical computation, it is desirable to select a smaller  $N_z$  when the species Z is a minor constituent of the space environment, or more precisely, is a smaller contributor to the effect being computed. In practice, this is done by establishing a heuristic selection probably  $p_z$  for each species in the environment. A simulation involving the tracking of N total incident ions is then conducted in this way

$$\frac{dR(E)}{dE} = \frac{4\pi^2 \rho^2}{N} \sum_{z=1}^{92} \sum_{i=1}^{p_z N} \left( \frac{\Phi_z(E_o(r_i))}{p_z \cdot n(E_o(r_i))} \right)$$

·MRED<sub>z</sub>(E<sub>o</sub>(r<sub>i</sub>), E). (4)

The selection of  $\mathbf{r}_i$  may be deterministic according to (3) or a uniform random number in the interval [0], [1]. Since the quantity  $N_z \approx p_z N$  is not guaranteed to be an integer, it must be rounded. This is done probabilistically so that it is possible to distribute the computation of (4) across a large number of independent processors.

The total rate of events that deposit energy greater than  $E_d$  is related to the differential rate by

$$R(E_d) = \int_{E_d}^{\infty} dE \frac{dR(E)}{dE}.$$

(5)

In practical calculations, between ten and 300 independent instances of (4) are computed in parallel, with each instance having an N value of order 10<sup>7</sup>. Individual events are given initial weights of  $\Phi_z(E_o(r_i))/(p_z \cdot n(E_o(r_i)))$ . The heuristic selection probability  $p_z$  is often taken to be the fifth root of the relative total abundance of the ion Z in the space environment.

To further increase the quality of the data for nuclear reaction events, all nuclear reaction cross sections are artificially increased by a factor  $\eta$ , which is typically chosen to be  $\approx 200$ . If the primary ion in an event produces a nuclear reaction, the total weight of the event is reduced by a factor of  $\eta$  from its initial value given above. As long as the use of the  $\eta$  factor does not materially alter (by < 5% as our typical criteria) the number of events that *do not* experience nuclear reactions, the only effect on the final distribution is to reduce the variance in the region of rare, large-energy-deposition, nuclear-reaction events.

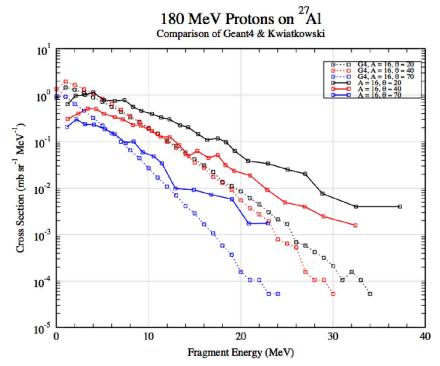

MRED typically uses the Geant4 binary intra-nuclear collision cascade to determine the final state for ion-ion nuclear reactions. Alternatively, the Bertini model may be, and is often, used for comparison purposes. The binary cascade code has been validated by the Geant4 collaboration for ions up to atomic number Z = 6. Beyond this, its use is more speculative, although data have been presented by the code developers that suggest that it may be used with caution up to at least Z = 26 (Fe) [27]. The magnitude of the effects we observe are dependent upon the details of this model, and will become less uncertain from systematic error as on-going efforts to improve the underlying physics are completed. However, the rates of nuclear reaction events depend on reaction cross sections, which are less uncertain than final state configurations. Therefore, while the quantitative results may improve with time, the qualitative conclusions are not likely to change. In any event, the mass, direction and energy of heavy nuclear reaction fragments are critical to single event computations and achieving statistical accuracy in predicting these quantities is critical for performing accurate rate calculations.

### V. CONCLUSION

Primary ion LET is not sufficient to describe the observed trends in measured SEU cross section data for modern technologies. Experimental results on three SRAMs show multiple values for the SEU cross section when irradiated with particles that have the same LET but different mass and energy. MRED-based simulations provide insight by showing that one must include a detailed description of the variability of radiation events (e.g., nuclear reactions), as opposed to the classical single valued LET parameter, in order to develop a well-behaved description of the SEE response. This is true for most circuits; the contribution of reaction products to the event rate in the space radiation environment can dominate the response in certain cases or can be overwhelmed by the direct ionization contribution in others, depending on the sensitivity of the circuit to transient radiation events.

MRED-based predictions were shown to be in excellent agreement with the average observed SEU rate on NASA's MESSENGER mission to Mercury. A prediction from the traditional rate-prediction method (IRPP), which does not include the contribution from ion-ion reactions, underestimates the observed rate by two orders of magnitude. Ion-ion nuclear reactions have a significant impact on the observed event rate for circuits with high critical charge. This is most important for circuits that contain high-Z materials near sensitive structures. The quality and accuracy of predictions are directly related to the details of device and circuit structure that are available. However, as the results reported here demonstrate, even relatively crude approximations are often sufficient to produce reasonably accurate simulations that describe responses to irradiation.

In [2], we provided a recommendation on ion species and energy selection when large inconsistencies occurred in the measured cross section at a single LET value. The current work shows that tests over energy and species similar to that given in Table I, i.e., ion beams less than 40 MeV/u, are sufficient to provide estimates for error rates. However, the testing at the higher energies, e.g., 100 MeV/u, allowed us to conclude that indirect ionization contributes significantly to the error cross section.

Ion energy and species, as opposed to a single-value for the ion LET, is the key metric for assessing the SEU susceptibility

Fig. 9. Comparison of Geant4 and experimental results from [22] for 180 MeV protons on aluminum. Geant4 dramatically underestimates the fragment energy.

of certain modern technologies. Reaction products from ion-ion interactions are a key basic mechanism when studying SEUs. While the potential of these trends to increase SEU event rates is important, the implications are potentially catastrophic for hard failures like SEL or soft errors that have significant impact at the system level, e.g., single event functional interrupts.

## APPENDIX

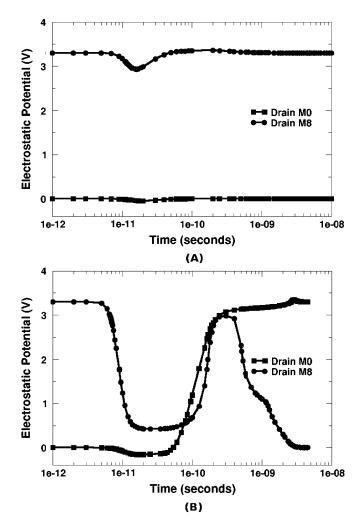

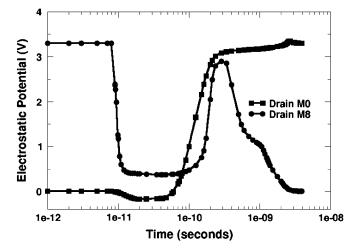

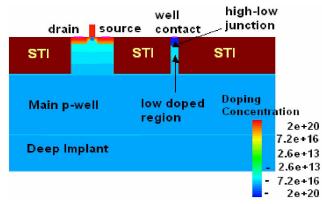

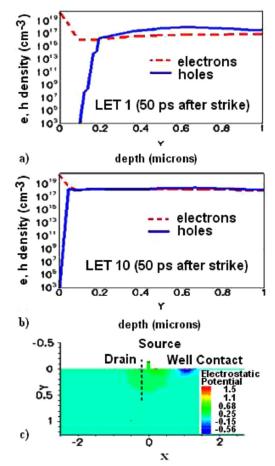

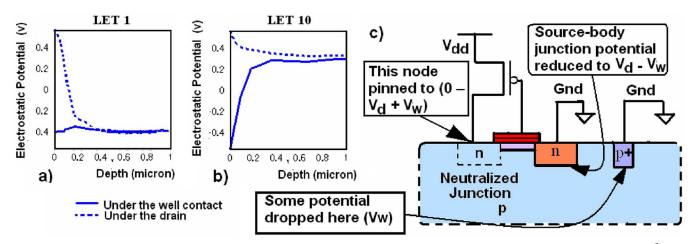

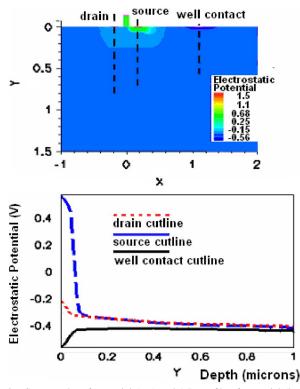

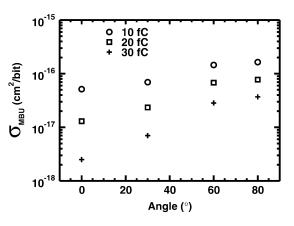

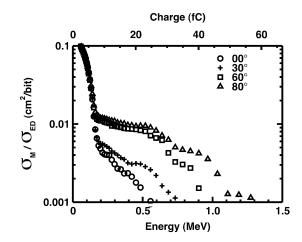

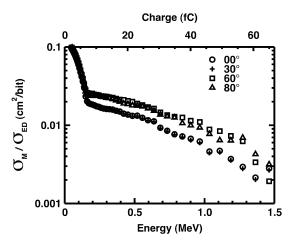

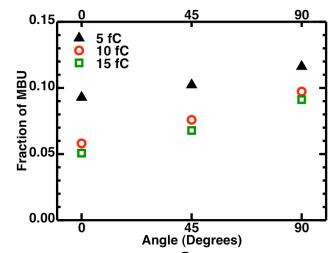

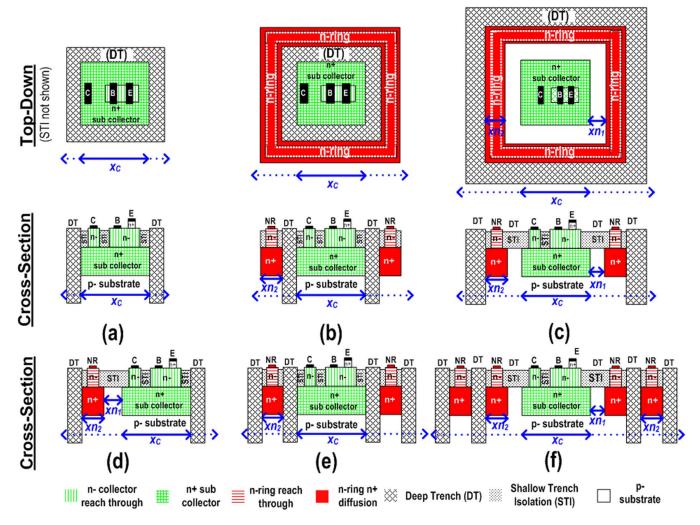

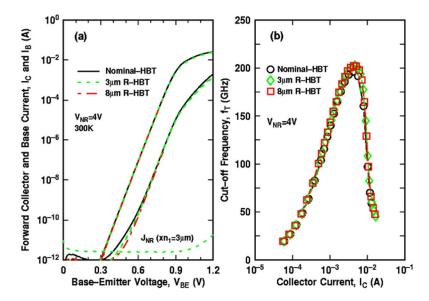

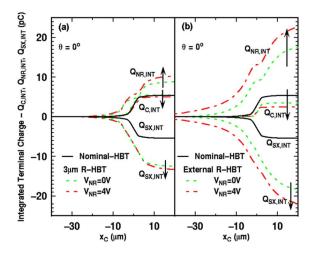

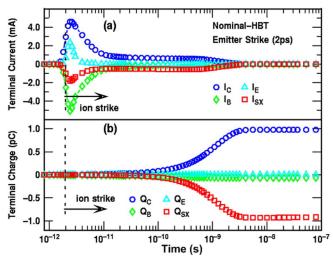

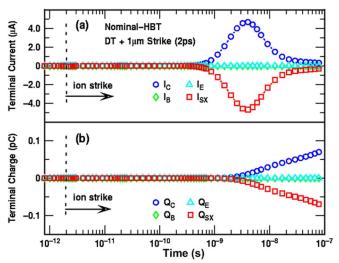

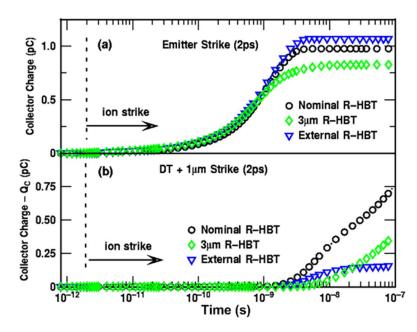

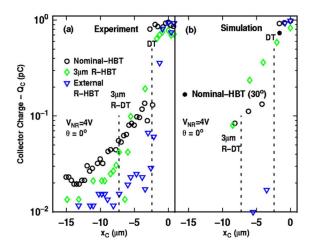

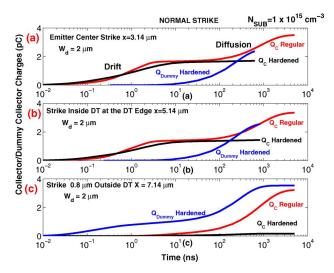

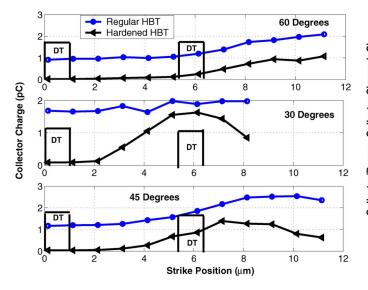

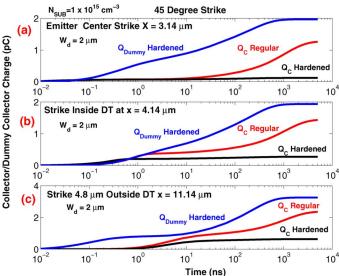

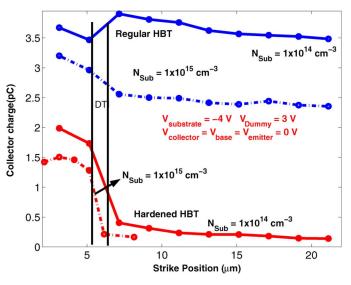

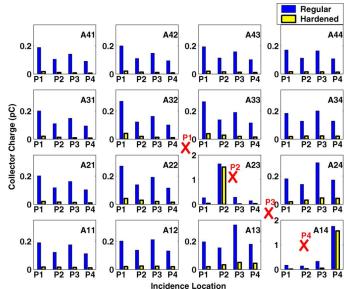

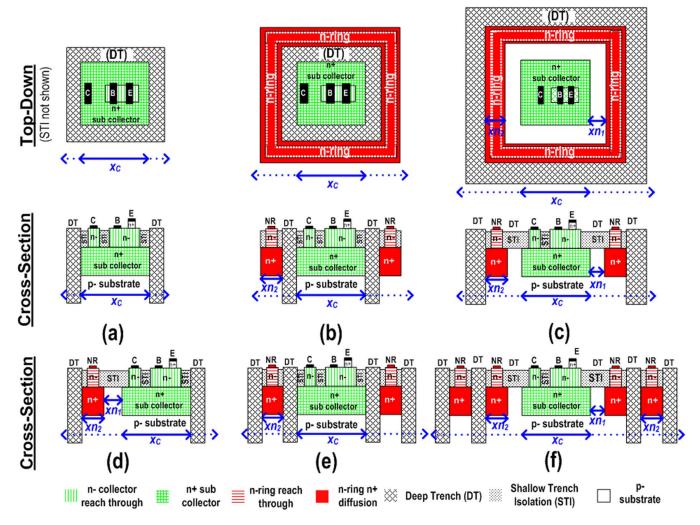

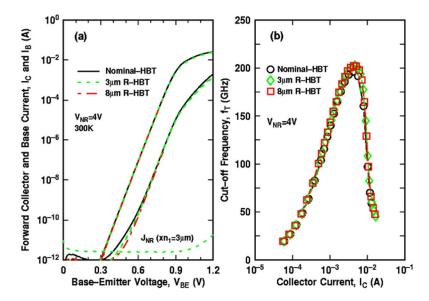

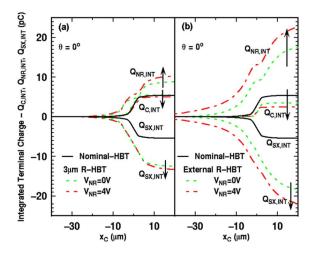

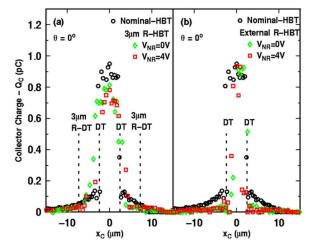

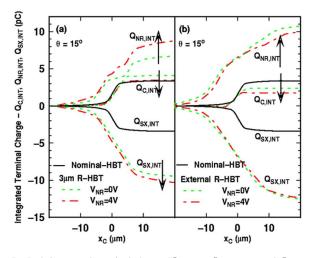

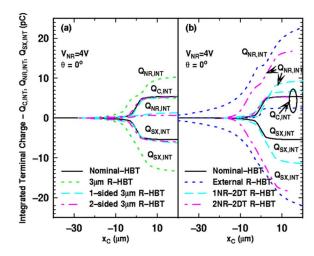

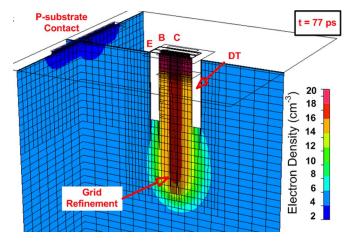

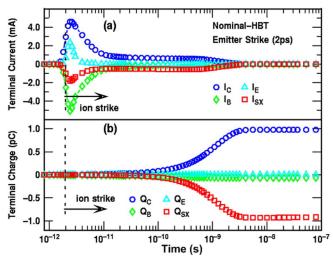

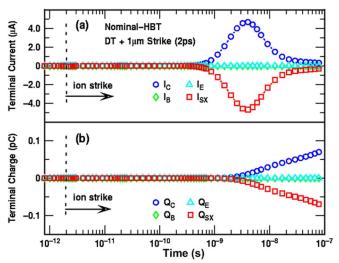

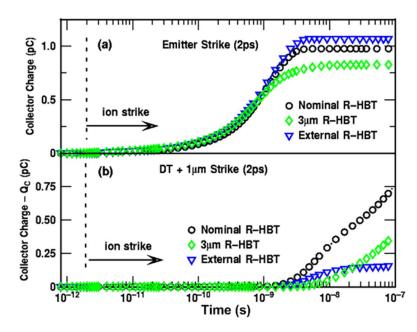

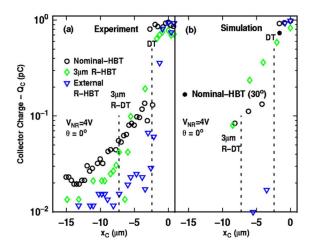

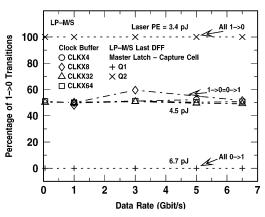

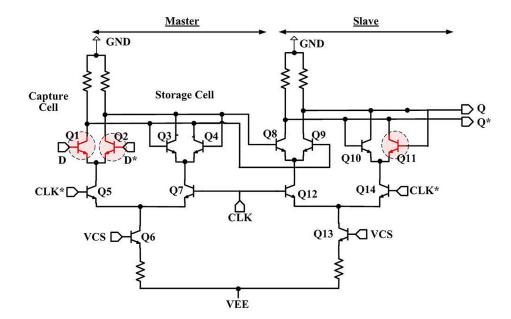

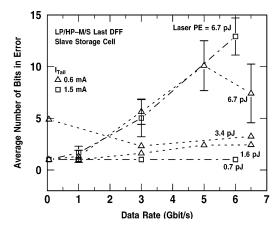

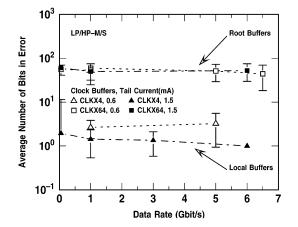

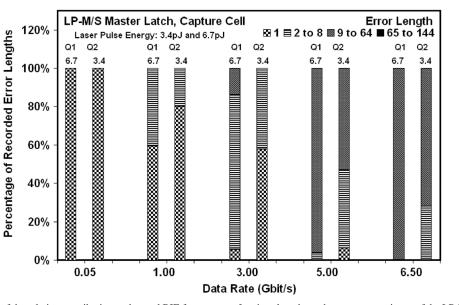

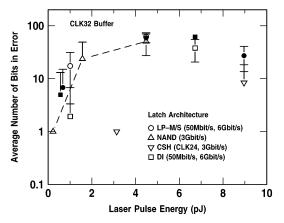

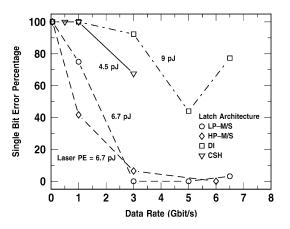

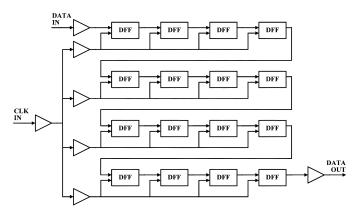

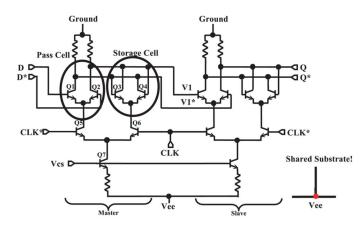

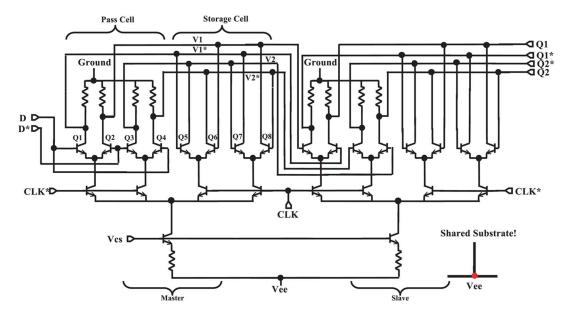

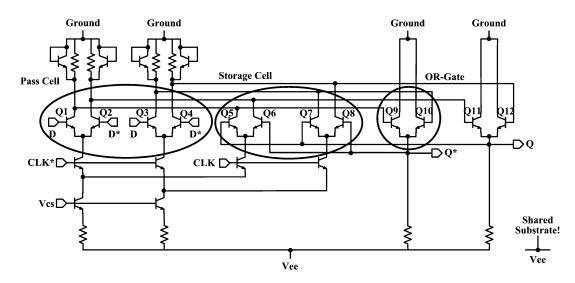

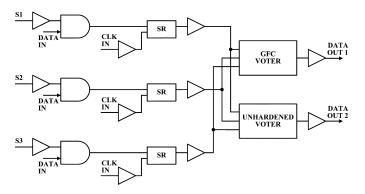

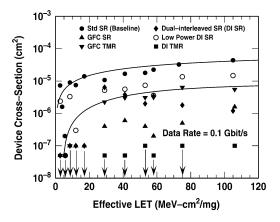

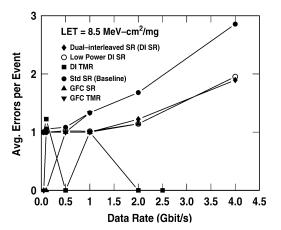

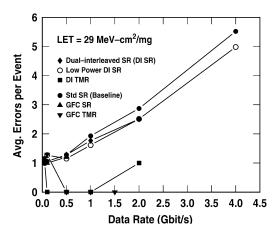

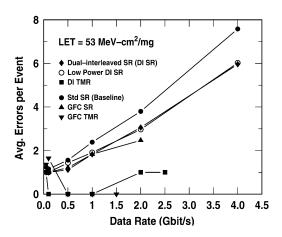

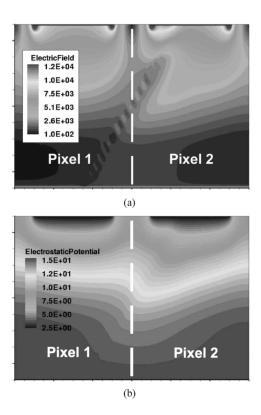

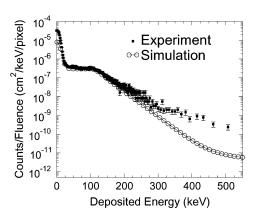

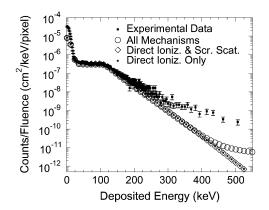

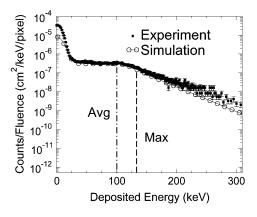

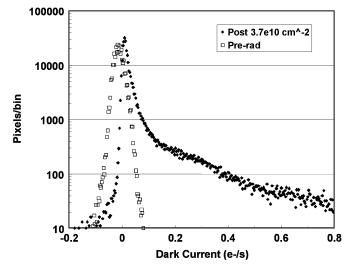

### SYSTEMATIC UNCERTAINTY IN GEANT4 NUCLEAR PHYSICS